Start - Działalność naukowa - Zespół systemów czasu rzeczywistego przewidywalnych czasowo PRET

Zespoły badawcze

Zespół systemów czasu rzeczywistego przewidywalnych czasowo PRET

Członkowie zespołu PRET

Dr hab. inż. Andrzej Pułka, Profesor Politechniki Śląskiej

Dr hab. inż. Adam Milik, Profesor Politechniki Śląskiej

Mgr inż. Ernest Antolak, doktorant

BADANIA NAUKOWE

Zespół powstał w 2008 r. jako efekt doświadczeń wyniesionych przez dr Andrzeja Pułkę ze współpracy z grupą CHESS prof. Edwarda A. Lee podczas pobytu na stażu naukowym w Uniwersytecie Kalifornijskim w Berkeley.

Główne zainteresowania badawcze zespołu koncentrują się na opracowaniu przewidywalnych czasowo wielozadaniowych systemów czasu rzeczywistego oraz wypracowania metod opisu, analizy i projektowania takich systemów w strukturach sprzętowych.

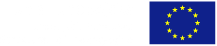

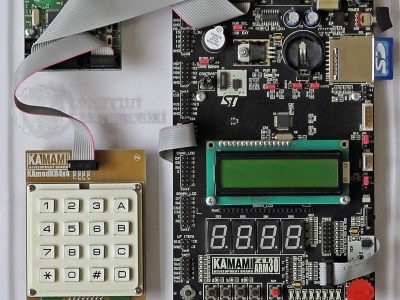

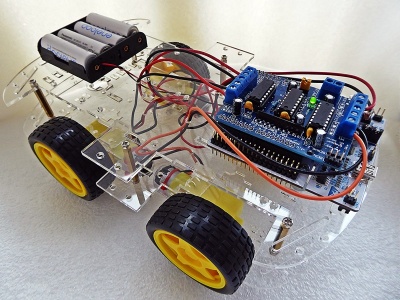

W ramach prac badawczych zespół opracował kilka własnych koncepcji realizacji elektronicznych systemów wbudowanych przewidywalnych-czasowo. Dotychczasowe badania były prowadzone na różnych poziomach abstrakcji od modelu systemowego (SystemC), poprzez modele behawioralne do niskopoziomowej realizacji sprzętowej w układach FPGA. W ramach prac opublikowano dotychczas 13 artykułów naukowych w czasopismach oraz na konferencjach naukowych, 9 tych prac jest notowanych w bazie WoS oraz Scopus. oraz zrealizowano jedną pracę doktorską. Aktualnie realizowana jest w tej tematyce kolejna praca doktorska, a badania rozszerzono o analizę energii rozpraszanej w systemie oraz efektywne harmonogramowanie zadań.

PUBLIKACJE

- A. Pułka, A. Milik: Multithread RISC Architecture Based on Programmable Interleaved Pipelining, Proceedings of IEEE ICECS 2009 Conference, Medina-Hammamet, TUNISIA, Dec. 13-16, pp. 647–650.

- A. Pułka, A. Milik: Dynamic Reconfiguration of Threads in Real–Time System Working on Precision Time Regime, Proceedings of the IEEE ICSES 2010 - International Conference on Signals and Electronic Systems, Gliwice, POLAND Sept.7-10, 2010, pp. 339–342.

- A. Pułka, A. Milik: Dynamiczna rekonfiguracja wątków w systemach czasu rzeczywistego pracujących w warunkach pełnej powtarzalności czasowej, Czasopismo „Elektronika” Nr 12 (2010), str. 40-43.

- A. Pułka, A. Milik: Dynamic Rescheduling of Tasks in Time Predictable Embedded Systems, Proceedings of the 11th IFAC Workshop on Programmable Devices and Embedded Systems PDeS 2012, Brno, Czech Republic, May 23-25, 2012, pp. 280–285.

- Golly Ł., Pułka A.: Multitask Real-Time Systems Modeling in SystemC. Proceedings of IEEE International Conference on Signals and Electronic Systems, ICSES 2012, Wrocław, Poland Sept.18-21 2012.

- Ł. Golly, A. Pułka: Timing analysis of multitask systems in SystemC environment, Czasopismo „Elektronika” Nr 2 (2013), str. 17–22.

- Ł. Golly, A. Pułka: Analysis of Timing Resources for Highly Predictable Real-Time Systems Models, Proceedings of MIXDES 2013 – The 20th International Conference on Mixed Design of Integrated Circuits and Systems, Gdynia, POLAND June 16-18 2013, pp. 497–502.

- Ł. Golly, A. Pułka: Time predictable systems based on pipeline processor with interleaving of hardware threads, Czasopismo „Elektronika” Nr 12 (2013), str. 36–40.

- Ł. Golly, A. Milik, A. Pułka: High Level Model of Time Predictable Multitask Control Unit, IFAC-PapersOnLine, Volume 48, Issue 4, 2015, 348–353, ISSN 2405-8963, http://dx.doi.org/10.1016/j.ifacol.2015.07.059.

- Ł. Golly, Współbieżne modelowanie przewidywalnych czasowo elektronicznych systemów wielozadaniowych w języku SystemC, Gliwice 2015, Praca doktorska pod kierunkiem dr hab. inż. Andrzeja Pułki obroniona w styczniu 2016r.

- A. Pułka, Ł. Golly: Some Issues Concerning Design Space Exploration in Time Predictable Embedded Systems, Proceedings of 2016 International Conference on Signals and Electronic Systems (ICSES), Krakow, 2016, pp. 231-236.

- E. Antolak and A. Pułka, "Flexible hardware approach to multi-core time-predictable systems design based on the interleaved pipeline processing," in IET Circuits, Devices & Systems, vol. 14, no. 5, pp. 648-659, 8 2020, doi: 10.1049/iet-cds.2019.0521.

- E. Antolak, A. Pułka - The Hierarchical model of a flexible predictable system for time critical data processing, Computer Networks 2020, Studia Informatica (zaakceptowane)

- E. Antolak and A. Pułka, "Energy-Efficient Task Scheduling in Design of Multithread Time Predictable Real-Time Systems," in IEEE Access, vol. 9, pp. 121111-121127, 2021, doi: 10.1109/ACCESS.2021.3108912.