Start - Kształcenie - Koła naukowe - NetFPGA

W semestrze letnim, w roku akademickim 2020/2021 oraz w semestrze zimowym, w roku akademickim 2021/2022 Studenckie Koło Naukowe Linuks i Wolne Oprogramowanie otrzymało dofinansowanie na realizację projektu pt.: "Przełącznik sieciowy z mechanizmem aktywnego zarządzania pakietami z wykorzystaniem specjalistycznego układu opartego o macierz programowalną FPGA"

Serdecznie gratulujemy sukcesów studentce zaangażazowanej w realizację projektu - Pani Marcie Szczygieł.

Spis treści

Instrukcja prezentuje kolejne kroki jakie należy wykonać, aby przygotować środowisko do budowy i uruchamiania projektów stworzonych na uniwersytecie w Cambridge dostępnych pod adresem: NetFPGA.

W repozytorium Github zawierającym projekty NetFPGA znajdują się następujące projekty:

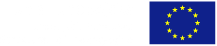

Programy dla macierzy programowalnej FPGA w projektach NetFPGA posiadają przedstawioną na rysunku 1 strukturę. Blok Output Port Lookup zależny jest od wybranego projektu.

Rys 1: Schemat blokowy projektów NetFPGA

Do uruchomienia przykładów należy posiadać:

Dla wyżej wymienionych wersji oprogramowania zostały przeprowadzone badania. Niemożliwe jest natomiast uruchomienie przykładów dla nowszych wersji oprogramowania, takich jak:

Budowanie i uruchamianie przykładów dla NetFPGA 1G CML, dostępnych na repozytorium link, możliwe jest tylko na archiwalnych systemach opartych o dystrybucję Red Hat, takich jak Fedora czy CentOS. W niniejszej instrukcji zaprezentowane zostało uruchomienie środowiska na systemie Fedora 20. Obraz instalatora systemu dostępny jest pod adresem: link.

Instalację systemu należy przeprowadzić tak, aby partycja administratora (root) posiadała minimalnie 50 GB pamięci. Podczas instalacji można pominąć tworzenie użytkowników, gdyż wszystkie prace będą wykonywane z konta użytkownika root.

Aby oprogramowanie oraz jego budowa wykonana została poprawnie wszystkie czynności związane z obsługą repozytorium powinny zostać przeprowadzone z konta administratora (root). Po uruchomieniu systemu należy logować się na użytkownika root.

Po przeprowadzeniu instalacji systemu Fedora 20 należy zaktualizować adresy repozytoriów dla instalatora pakietów YUM. W tym celu należy zamienić poszczególne adresy w plikach. Przygotowane pliki pod system Fedora 20 zostały dodane do instrukcji w katalogu 1.yum.repo:

Po zaktualizowaniu adresów repozytorium dla menadżera pakietów YUM należy zaktualizować system oraz wszystkie zainstalowane w systemie pakiety za pomocą komendy: yum update Po przeprowadzeniu aktualizacji należy zainstalować wymagane pakiety do działania przykładów NetFPGA, takie jak: kompilator gcc, bibliotekę do obsługi interfejsu JTAG, itd. Poniższa komenda umożliwia instalację wszystkich potrzebnych pakietów:

yum install gcc gcc-c++ minicom libusb-devel glibc.i686 scapy xterm libXp java-devel libnet-devel iperf screen openmotif ncurses-compat-libs make git minicom '*stdc*' libsigc++ libsigc++.i686 qt.i686 qt qgit dnf install lrzsz gedit firefox gtkterm

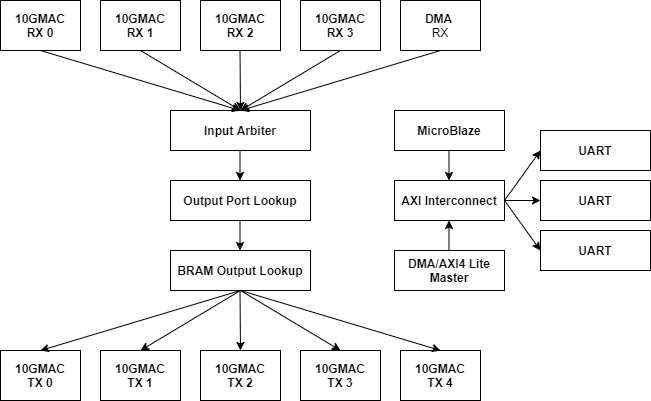

Do poprawnego działania oprogramowania Xilinx oraz bibliotek należy wyłączyć zabezpieczenia Security-Enhanced Linux. W tym celu należy otworzyć plik selinux za pomocą komendy:

gedit /etc/sysconfig/selinux

W pliku tym należy zmienić enforcing mode na permissive w następujący sposób:

SELINUX=permissive

Na rysunku 2 przedstawiono poprawny plik.

Rys 2: Wyłączenie zabezpieczeń SEL

Oprogramowanie Xilinx Design Suite 14.7 dostępne jest pod adresem: link

Po pobraniu instalatora należy rozpakować archiwum za pomocą interfejsu GUI lub następującej komendy:

tar -xvf Xilinx_ISE_DS_Lin_14.7_1015_1.tar

Następnie należy przejść do rozpakowanego folderu i uruchomić program instalacyjny za pomocą skryptu xsetup:

cd Xilinx_ISE_DS_Lin_14.7_1015_1

./xsetup

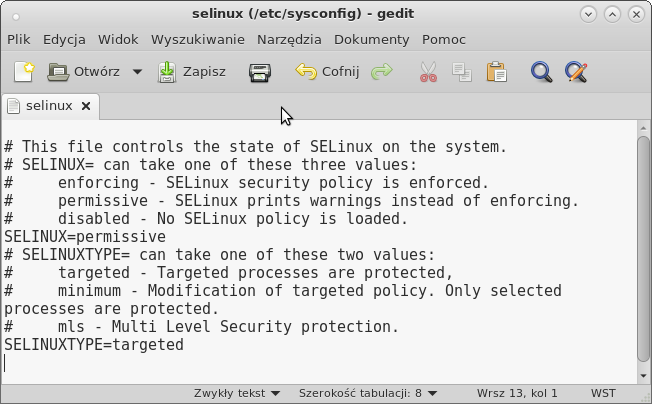

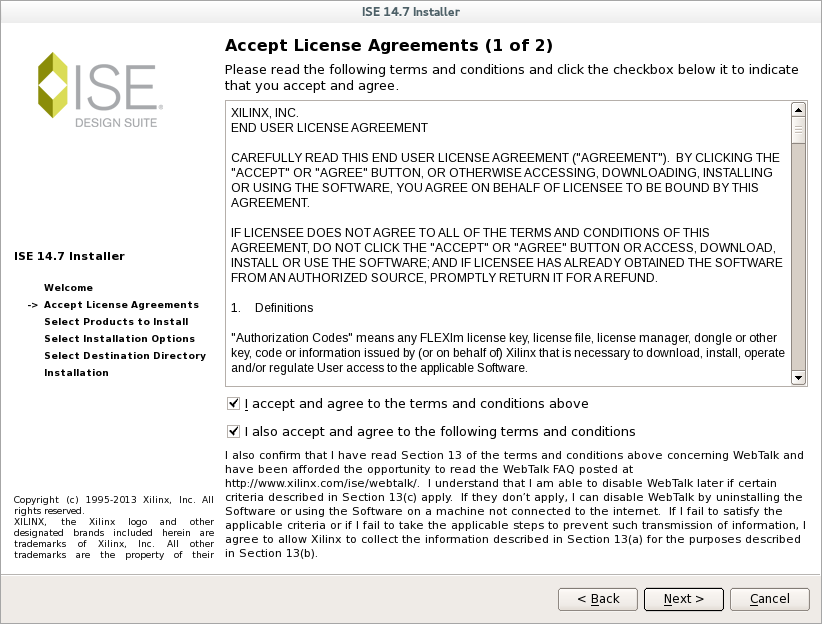

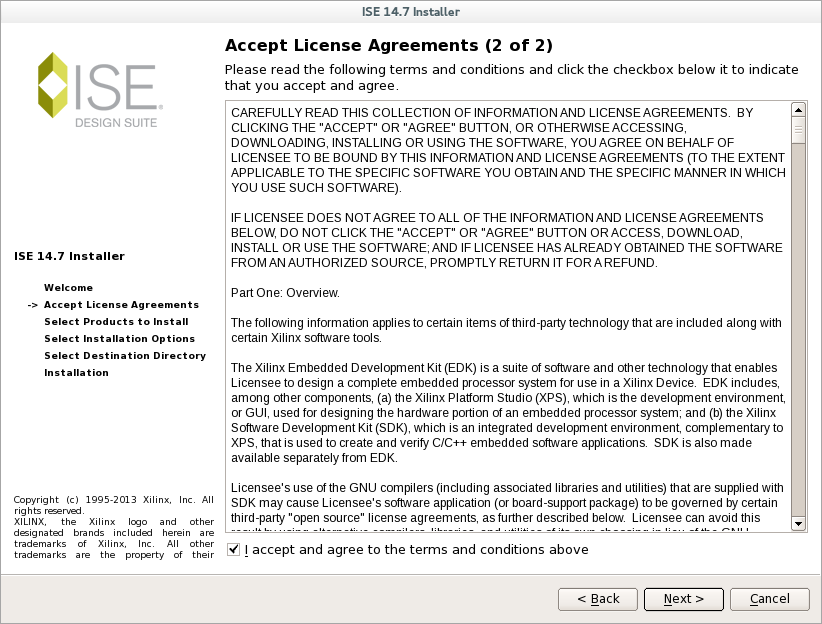

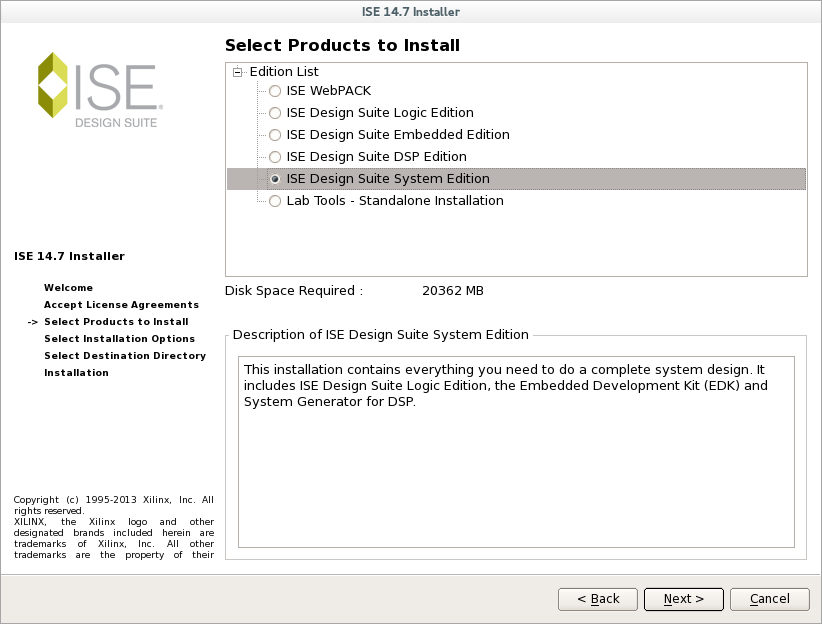

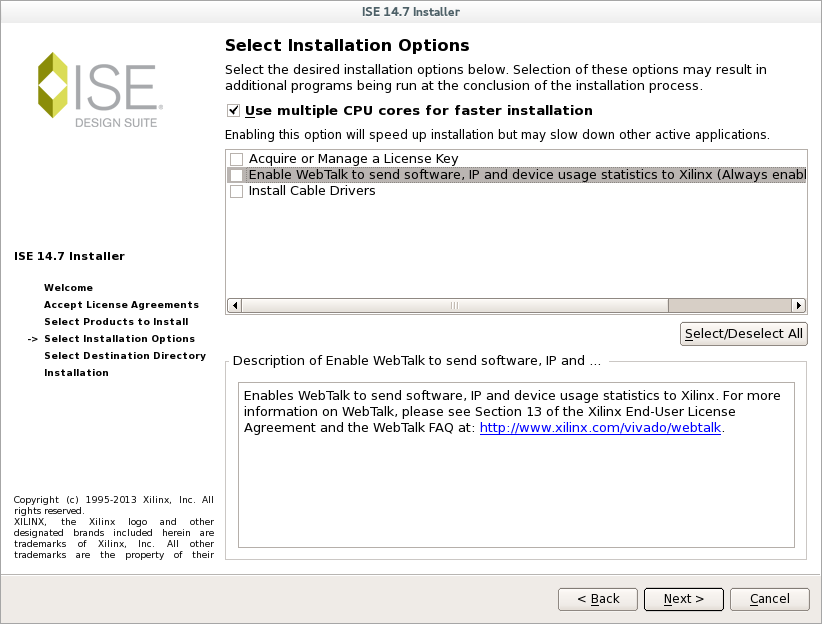

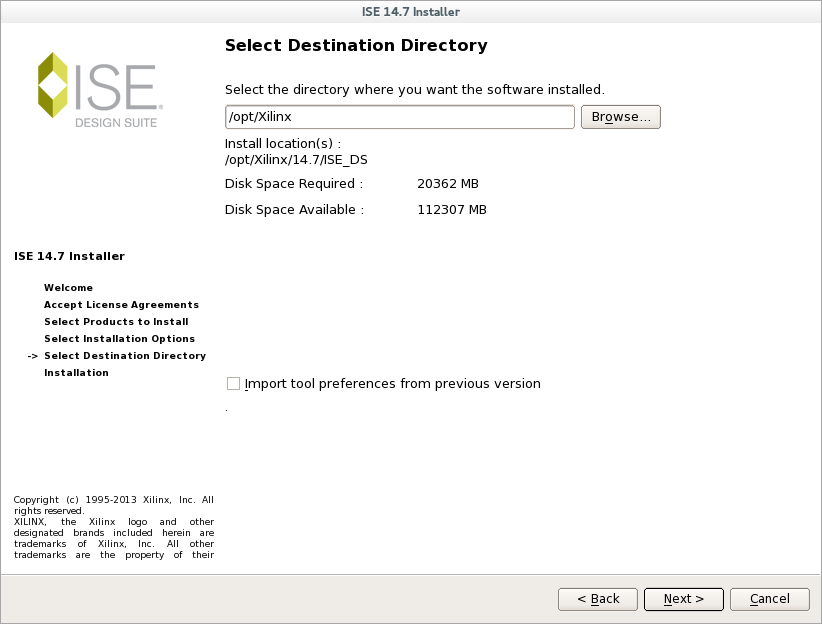

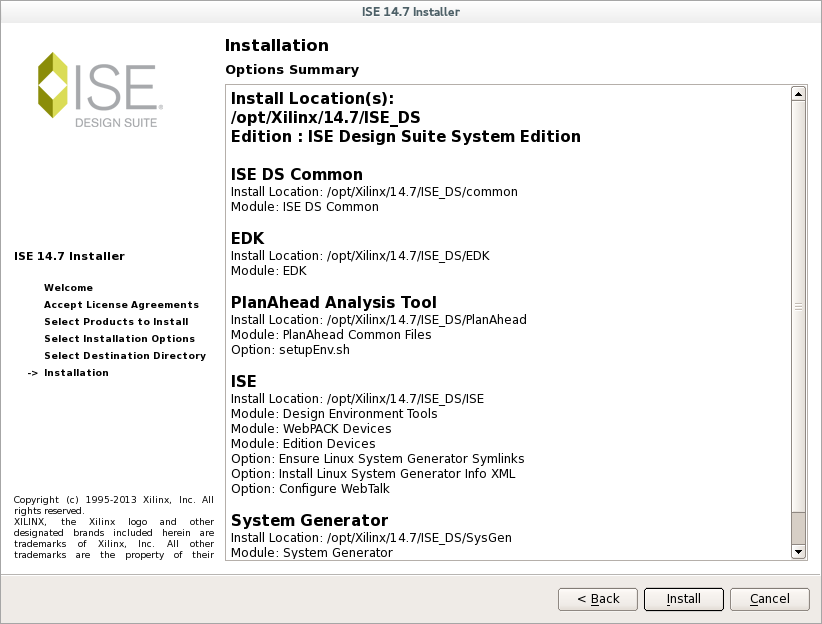

Podczas instalacji należy odznaczyć instalację sterowników Install Cable Drivers oraz Import tool preferences from previous version. Wszystkie okna zawierające kolejne kroki instalacji zostały zamieszczone na rysunkach 3, 4, 5 i 6.

Rys 3: Instalacja Xilinx ISE Design Suite 14.7

Rys 4: Instalacja Xilinx ISE Design Suite 14.7

Rys 5: Instalacja Xilinx ISE Design Suite 14.7

Rys 6: Instalacja Xilinx ISE Design Suite 14.7

Oprogramowanie Vivado Design Suite 15.2 dostępne jest pod adresem: link

Po pobraniu instalatora należy rozpakować archiwum za pomocą interfejsu GUI lub następującej komendy:

tar -xvf Xilinx_Vivado_SDK_Lin_2015.2_0626_1.tar.gz

Następnie należy przejść do rozpakowanego folderu i uruchomić program instalacyjny za pomocą skryptu xsetup:

cdXilinx_Vivado_SDK_Lin_2015.2_0626_1

./xsetup

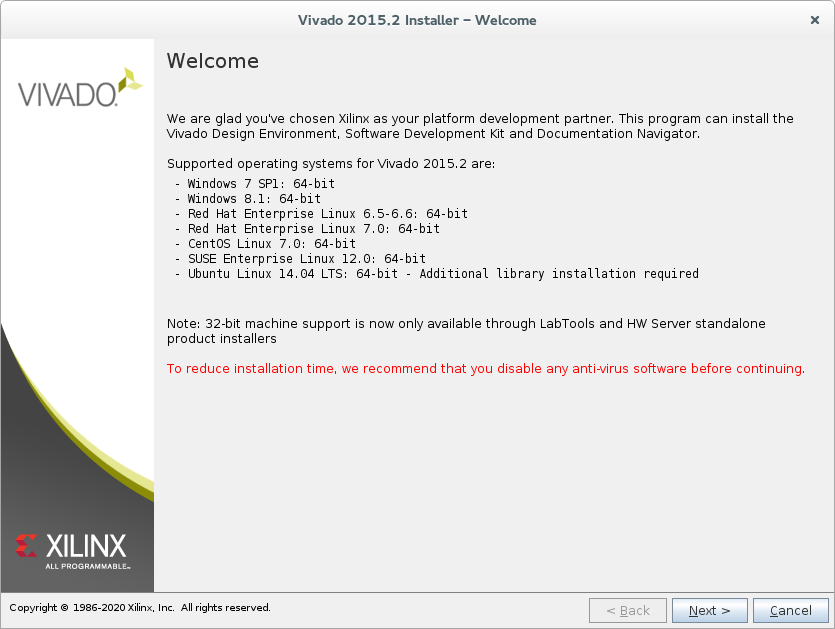

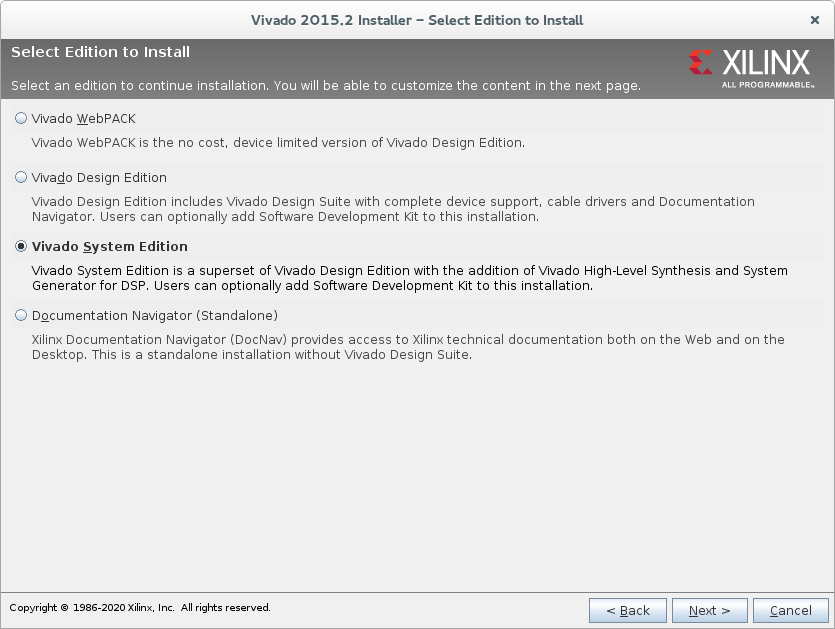

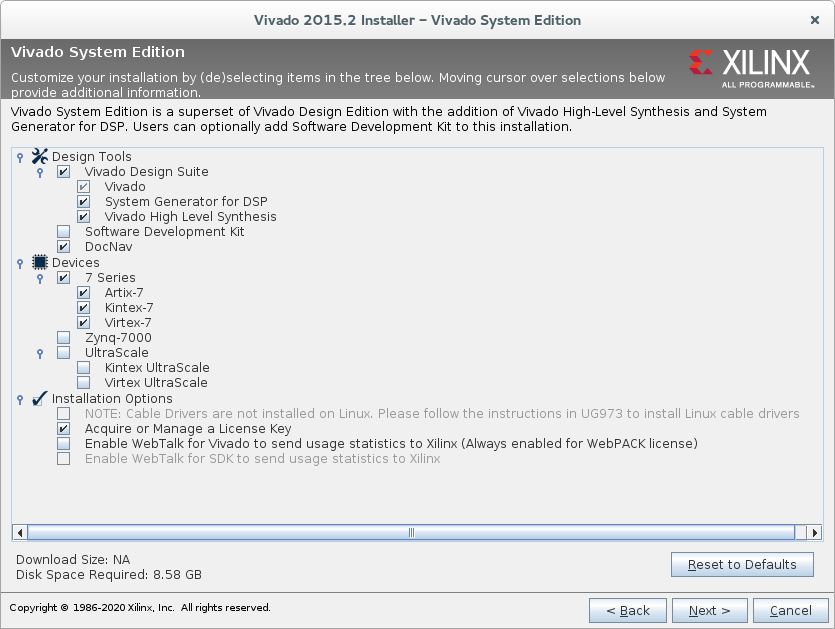

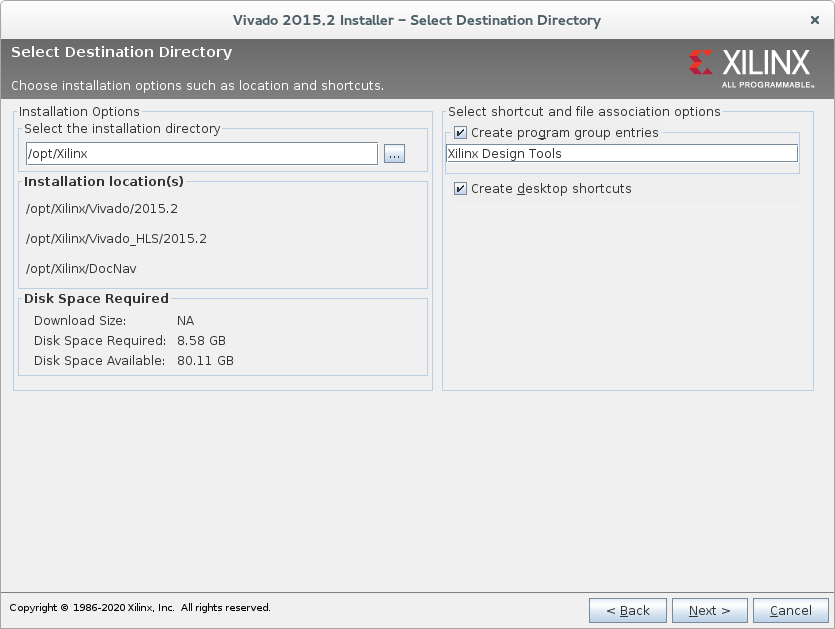

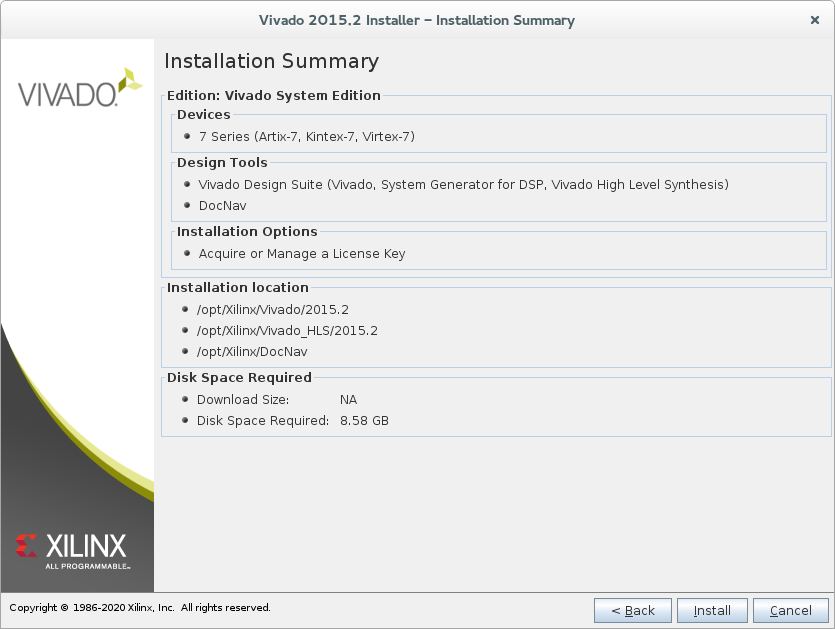

Podczas instalacji należy odznaczyć instalację sterowników: Install Cable Drivers. Ponadto można odznaczyć instalację oprogramowania dla Zynq czy UltraScale, gdyż te funkcjonalności nie będą wykorzystywane. Wszystkie okna zawierające kolejne kroki instalacji zostały zamieszczone na rysunkach 7, 8 i 9.

Rys 7: Instalacja Vivado Design Suite 15.2

Rys 8: Instalacja Vivado Design Suite 15.2

Rys 9: Instalacja Vivado Design Suite 15.2

Do poprawnego zaprogramowania urządzenia potrzebne są sterowniki dostępne pod adresem: link

Po pobraniu należy je rozpakować, zbudować i skopiować do folderu ze sterownikami. Można to wykonać za pomocą następujących komend:

tar -xvf usb-driver-HEAD-2d19c7c.tar.gz

cd usb-driver-HEAD-2d19c7c

source /opt/Xilinx/14.6/ISE_DS/settings64.sh\

make

./setup_pcusb

cp libusb-driver.so /usr/local/lib/libusb-jtag-driver.so

Dostęp do repozytorium NetFPGA można uzyskać po wysłaniu prośby o dostęp za pomocą formularza rejestracyjnego dostępnego pod adresem: link

Po otrzymaniu dostępu do repozytorium należy je pobrać z serwisu Github lub za pomocą komendy. Najlepiej poniższą komendę wykonać w bazowym folderze administratora /root/:

git clone https://github.com/NetFPGA/NetFPGA-1G-CML-live.git

Do budowy i programowania projektów NetFPGA wymagane jest poprawne skonfigurowanie środowiska. Środowisko powinno być skonfigurowany w taki sposób, aby oprogramowanie Xilinx, biblioteki oraz skróty do projektów były dostępne z poziomu linii poleceń. W konsoli, w której będą budowane projekty należy uruchomić następujące komendy:

source /opt/Xilinx/14.7/ISE_DS/settings64.sh

source /opt/Xilinx/Vivado/2015.2/settings64.sh

export NF_ROOT=/root/NetFPGA-1G-CML-live/

export NF_DESIGN_DIR=${NF_ROOT}/projects/loopback_test_nf1_cml

export NF_WORK_DIR=/root/tmp/

export PYTHONPATH= ${NF_ROOT}/lib/python:${NF_DESIGN_DIR}/lib/Python:${NF_ROOT}/tools/scripts:}

export LD_LIBRARY_PATH= ${NF_ROOT}/lib/java/NetFPGAFrontEnd/bin:${LD_LIBRARY_PATH}}

export XILINXD_LICENSE_FILE=licencja

W przypadku, gdy folder z repozytorium NetFPGA nie znajduje się w /root/ należy zmienić ścieżkę dostępu. W przygotowanych skryptach początkowo wybranym projektem, który będzie kompilowany jest loopback_test_nf1_cml. Zmiana projektu wykonywana jest poprzez zmianę wartości zmiennej NF_DESIGN_DIR.

Po wywołaniu komend z rozdziału 1.6.2 możliwe jest zbudowanie podstawowych bibliotek wykorzystywanych w projektach NetFPGA. Do budowy wykorzystywany jest system make. W celu zbudowania bibliotek należy przejść do głównego katalogu projektu i wywołać komendę make:

cd $NF_ROOT

make

Wykonanie kolejnych kroków instrukcji powinno umożliwić poprawną budowę projektów, jednak podczas budowy może wystąpić niewykryty podczas testowania błąd. W celu jego wykrycia należy sprawdzić wygenerowany w konsoli log pod względem błędów.

Projekty Learning CAM Switch oraz Reference Router bazują na podobnej logice działania. Projekty te wykorzystują pamięć adresowaną (CAM). Do jej poprawnego budowania należy pobrać xapp1151.

Oprogramowanie to dostępne jest na forum Xilinx pod adresem: link

Dokumentacja oprogramowania xapp1151_Param_CAM dostępna jest pod adresem: link

Aby użyć pobranego oprogramowania należy je rozpakować i wykonać następujące kroki:

unzip xapp1151_Param_CAM.zip

cd xapp1151_cam_v1_1/

export NF_ROOT=/root/NetFPGA-1G-CML-live/

export NF_DESIGN_DIR=${NF_ROOT}/projects/reference_switch_nf1_cml

cp -r $NF_DESIGN_DIR/patches .

cd patches/

gedit cam_patch.sh

patch /root/Pobrane/xapp1151_cam_v1_1/implement/CustomizeWrapper.pl CustomizeWrapper.pl.patch

patch /root/Pobrane/xapp1151_cam_v1_1/implement/vhdl_xst.scr vhdl_xst.scr.patch

patch /root/Pobrane/xapp1151_cam_v1_1/src/vhdl/cam_pkg.vhd cam_pkg.vhd.patch

patch /root/Pobrane/xapp1151_cam_v1_1/src/vhdl/cam_control.vhd cam_control.vhd.patch

patch /root/Pobrane/xapp1151_cam_v1_1/src/vhdl/cam_mem_blk.vhd cam_mem_blk.vhd.patch

patch /root/Pobrane/xapp1151_cam_v1_1/src/vhdl/cam_mem_blk_extdepth_prim.vhd cam_mem_blk_extdepth_prim.vhd.patch

patch /root/Pobrane/xapp1151_cam_v1_1/src/vhdl/cam_rtl.vhd cam_rtl.vhd.patch

sh cam_patch.sh

cd ../implement/

source /opt/Xilinx/14.7/ISE_DS/settings64.sh

xilperl CustomizeWrapper.pl

Odpowiedzi dla projektu Learning CAM Switch:

Enter the FPGA base architecture to target: kintex7

Input the CAM data width: 48

Input the CAM depth: 16

Enter the CAM memory type to implement: 1

Will the CAM be write-able (WE pin)?: y

Use a MIF file to initialize the memory contents?: n

Choose what type of encoding the MATCH_ADDR port will have: 0

For Binary Encoded or Single Match Unencoded MATCH_ADDR, output lowest address match or highest address match?: 0

Please select the optional features to be implemented: Simultaneous Read/Write: y

Register Outputs: n

Please select from the following optional input ports: Enable (EN) : n

Please select from the following optional output ports: Multiple Match Flag (MULTIPLE_MATCH): n

Single Match Flag (SINGLE_MATCH): n

Read Warning Flag (READ_WARNING): n

Odpowiedzi dla projektu Reference Router:

Enter the FPGA base architecture to target: kintex7

Input the CAM data width: 32

Input the CAM depth: 32

Enter the CAM memory type to implement: 1

Will the CAM be write-able (WE pin)?: y

Use a MIF file to initialize the memory contents?: n

Choose what type of encoding the MATCH_ADDR port will have: 1

For Binary Encoded or Single Match Unencoded MATCH_ADDR, output lowest address match or highest address match?: 0

Please select the optional features to be implemented: Simultaneous Read/Write: y

Register Outputs: n

Please select from the following optional input ports: Enable (EN) : n

Please select from the following optional output ports: Multiple Match Flag (MULTIPLE_MATCH): n

Single Match Flag (SINGLE_MATCH): n

Read Warning Flag (READ_WARNING): n

gedit vhdl_xst.scr

C_FAMILY : string := kintex7;

C_MEM_TYPE : integer := 1;

C_WIDTH : integer := 48;

C_DEPTH : integer := 16;

C_ADDR_TYPE : integer := 0;

C_MATCH_RESOLUTION_TYPE : integer := 0;

C_TERNARY_MODE : integer := 0;

C_HAS_WE : integer := 1;

C_MEM_INIT : integer := 0;

C_HAS_CMP_DIN : integer := 1;

C_REG_OUTPUTS : integer := 0;

C_HAS_EN : integer := 0;

C_HAS_MULTIPLE_MATCH : integer := 0;

C_HAS_SINGLE_MATCH : integer := 0;

C_HAS_READ_WARNING : integer := 0;

C_FAMILY : string := kintex7;

C_MEM_TYPE : integer := 0;

C_WIDTH : integer := 32;

C_DEPTH : integer := 32;

C_ADDR_TYPE : integer := 1;

C_MATCH_RESOLUTION_TYPE : integer := 0;

C_TERNARY_MODE : integer := 1;

C_HAS_WE : integer := 1;

C_MEM_INIT : integer := 0;

C_HAS_CMP_DIN : integer := 1;

C_REG_OUTPUTS : integer := 0;

C_HAS_EN : integer := 0;

C_HAS_MULTIPLE_MATCH : integer := 0;

C_HAS_SINGLE_MATCH : integer := 0;

C_HAS_READ_WARNING : integer := 0;

xilperl RunXST.pl

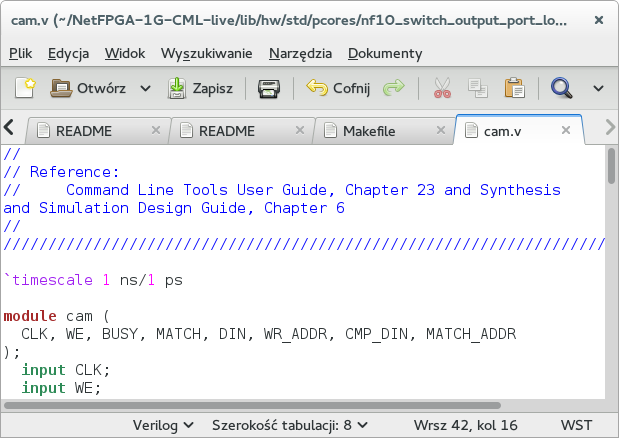

cd results netgen -sim -ofmt verilog cam.ngc

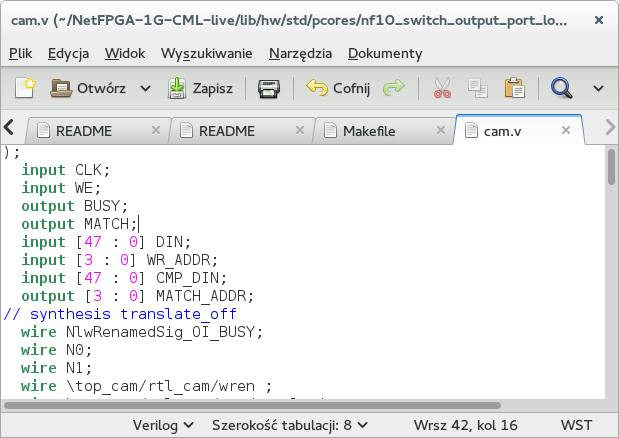

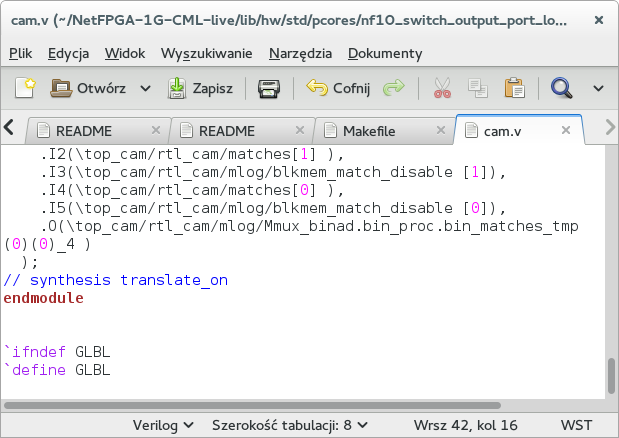

gedit cam.v

Rys 10: Zmiana nazwy modułu

// synthesis translate_off

Rys 11: Włączenie ignorowania kodu

// synthesis translate_on

Rys 12: Wyłączenie ignorowania kodu

mkdir -p $NF_ROOT/lib/hw/std/pcores/nf10_switch_output_port_lookup_v1_10_a/netlist

cp cam.ngc $NF_ROOT/lib/hw/std/pcores/nf10_switch_output_port_lookup_v1_10_a/netlist

cp cam.v $NF_ROOT/lib/hw/std/pcores/nf10_switch_output_port_lookup_v1_10_a/hdl/verilog

mkdir -p $NF_ROOT/lib/hw/std/pcores/nf10_router_output_port_lookup_v1_00_a/netlist

cp cam.ngc $NF_ROOT/lib/hw/std/pcores/nf10_router_output_port_lookup_v1_00_a/netlist

cp cam.v $NF_ROOT/lib/hw/std/pcores/nf10_router_output_port_lookup_v1_00_a/hdl/verilog

Po budowie podstawowych bibliotek opisanych w rozdziale 1.6.3 oraz przygotowaniu bibliotek dla projektów Learning CAM Switch oraz Reference Router, opisanych w rozdziale 1.6.4, można przystąpić do budowy projektów. W tym celu należy przejść do katalogu z projektem i wywołać komendę make:

cd $NF_DESIGN_DIR

make

Po wykonaniu komendy powinien zostać stworzony plik konfiguracyjny macierz FPGA w folderze bitfiles.

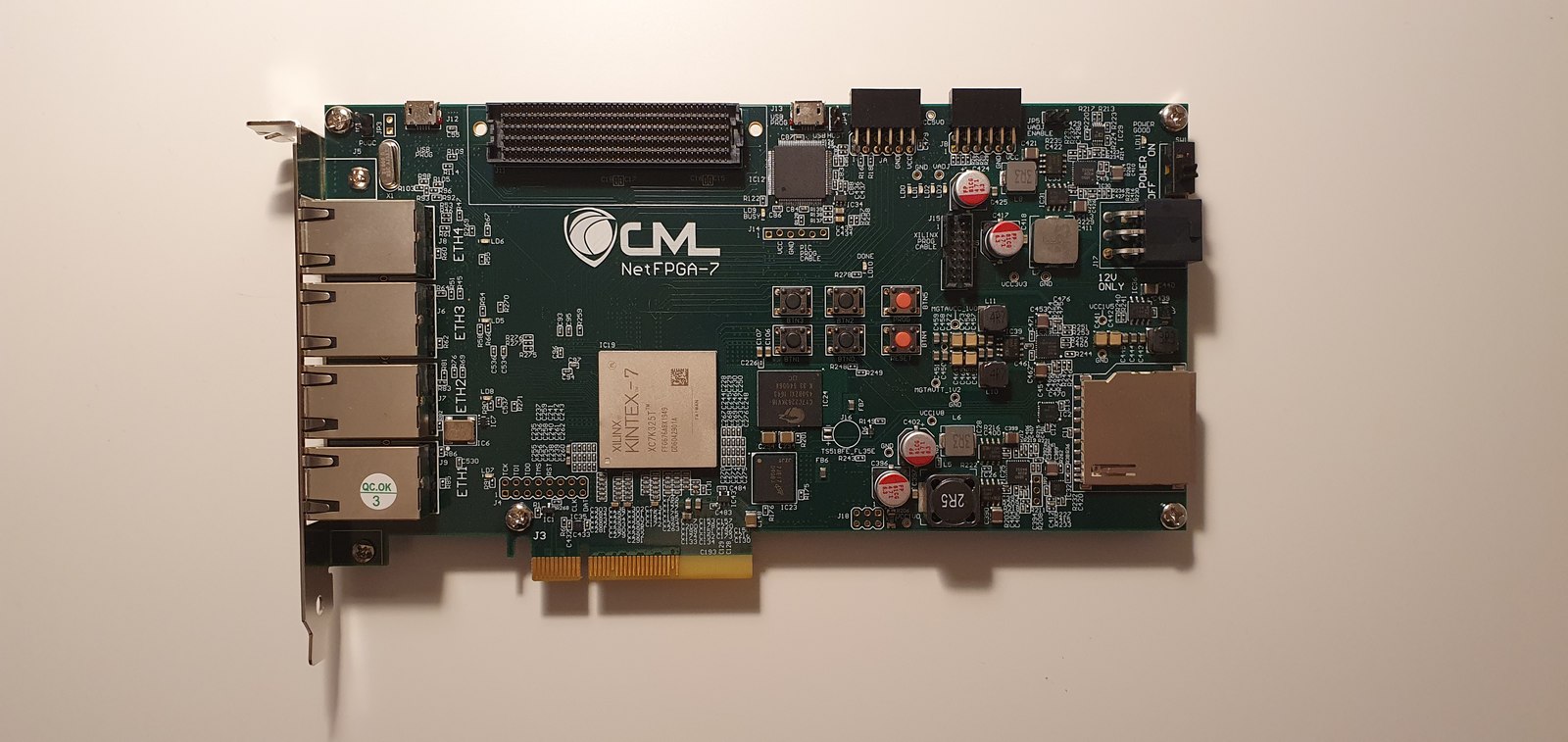

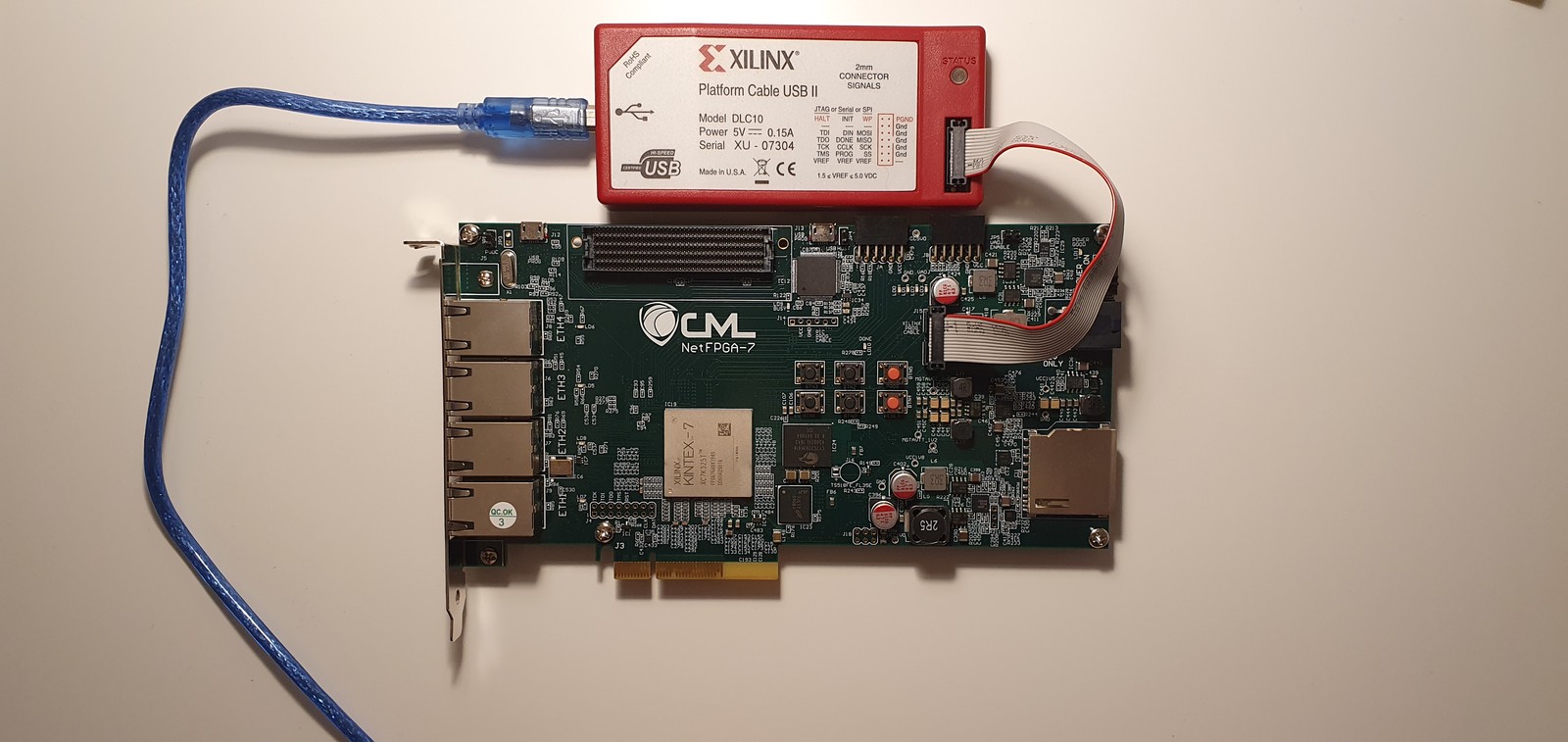

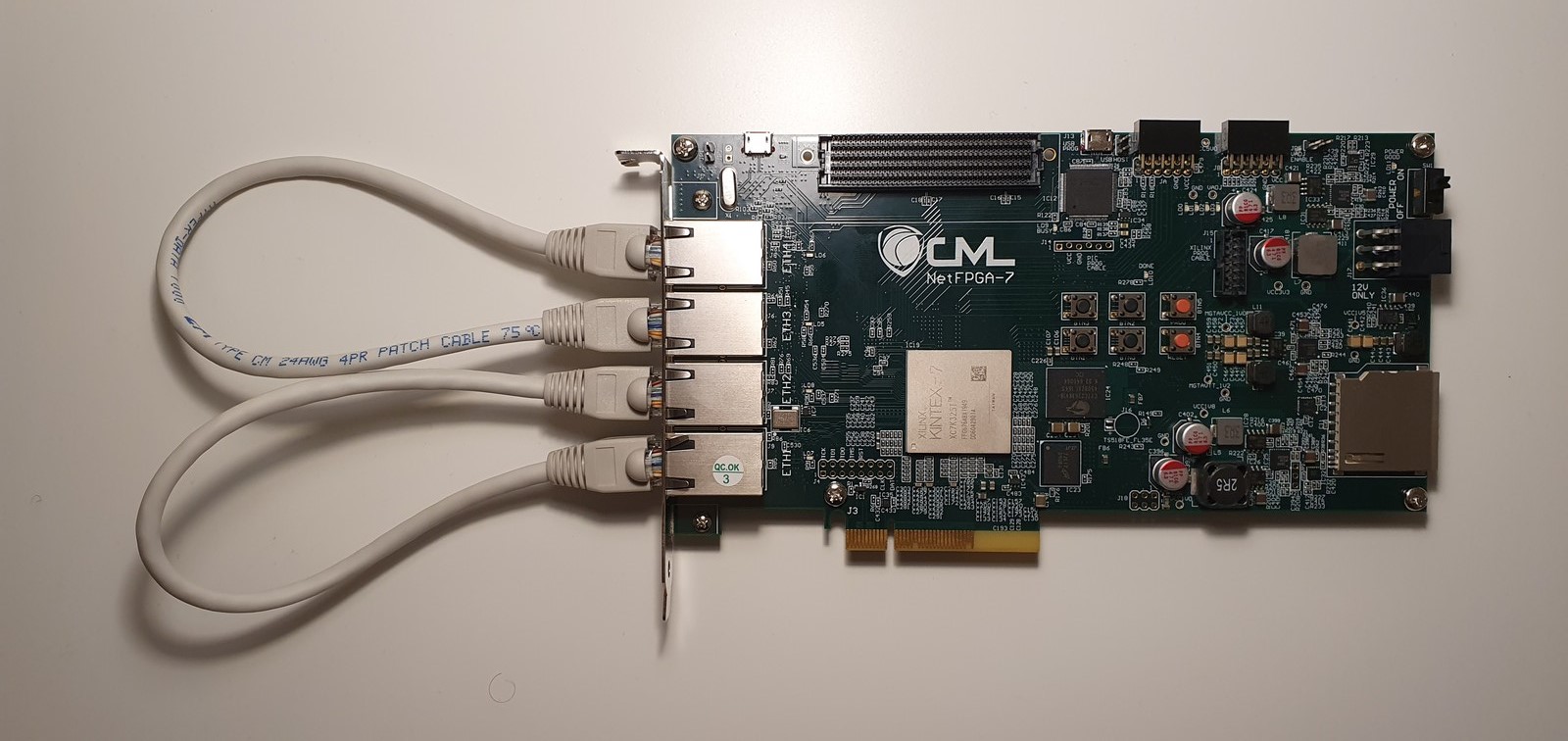

Rys 13: Układ NetFPGA 1G CML

Układ można używać jako wewnętrzne urządzenie PCI-E podłączone do płyty głównej komputera lub jako zewnętrze urządzenie. W przypadku, gdy urządzenie nie jest stosowane jako karta sieciowa lub router nie musi być ono podłączone do złącza PCI.

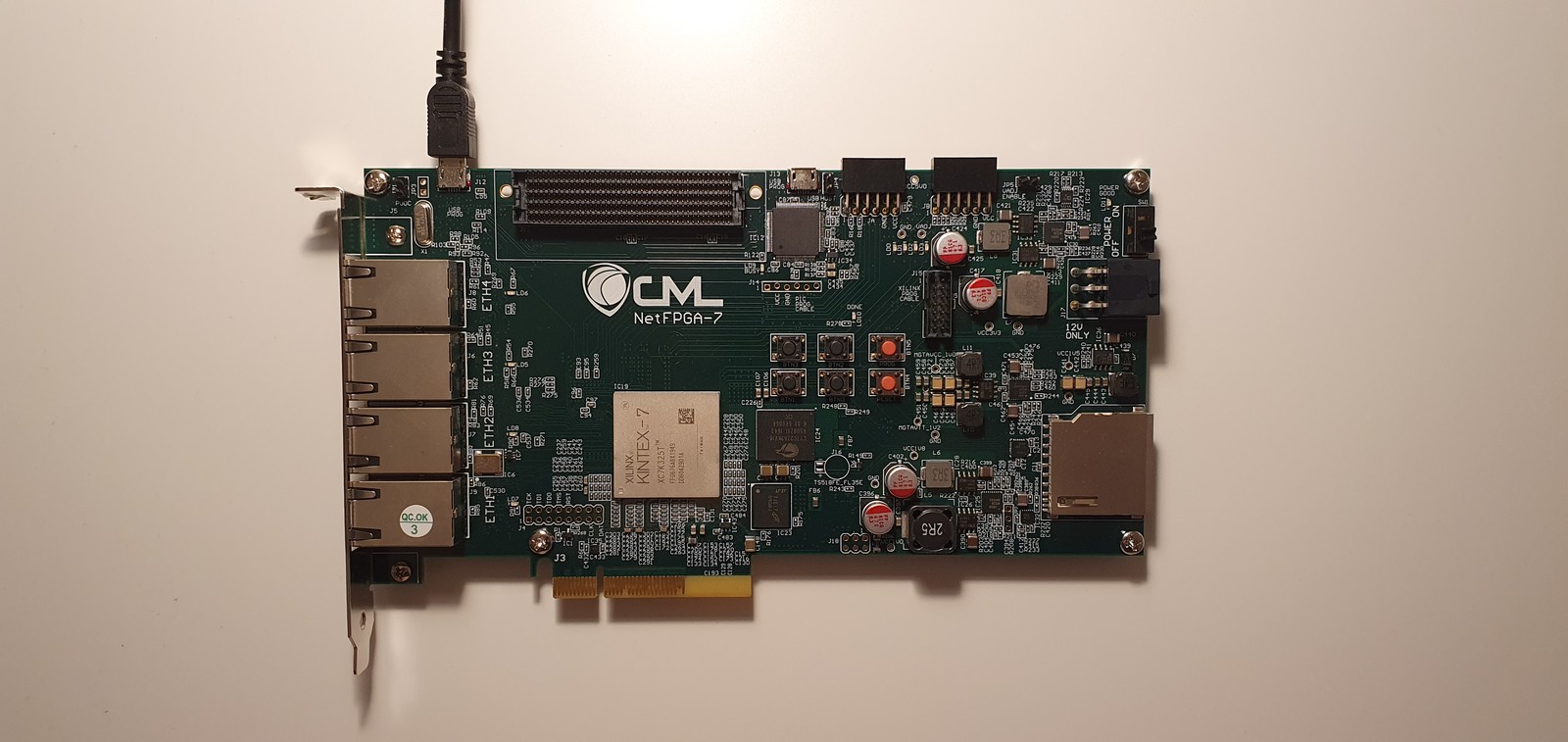

Do programowania można wykorzystać programator zewnętrzny lub wewnętrzny. Na rysunku 14 został przedstawiony sposób podłączenia programatora zewnętrznego, a na rysunku 15 programatora wewnętrznego.

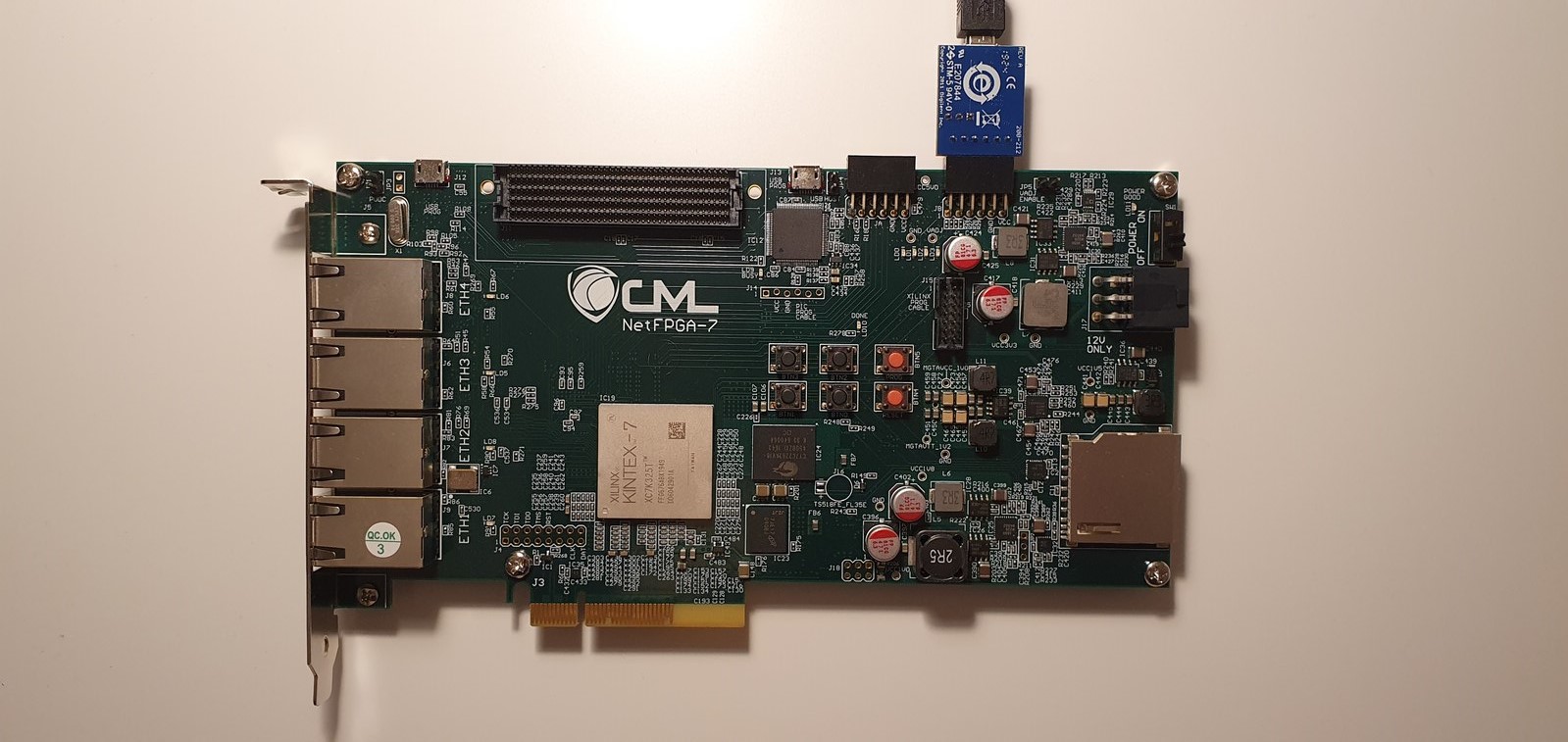

Rys 14: Podłączenie kabla micro USB do wbudowanego programatora układu NetFPGA 1G CML

Rys 15: Podłączenie zewnętrznego programatora do układu NetFPGA 1G CML

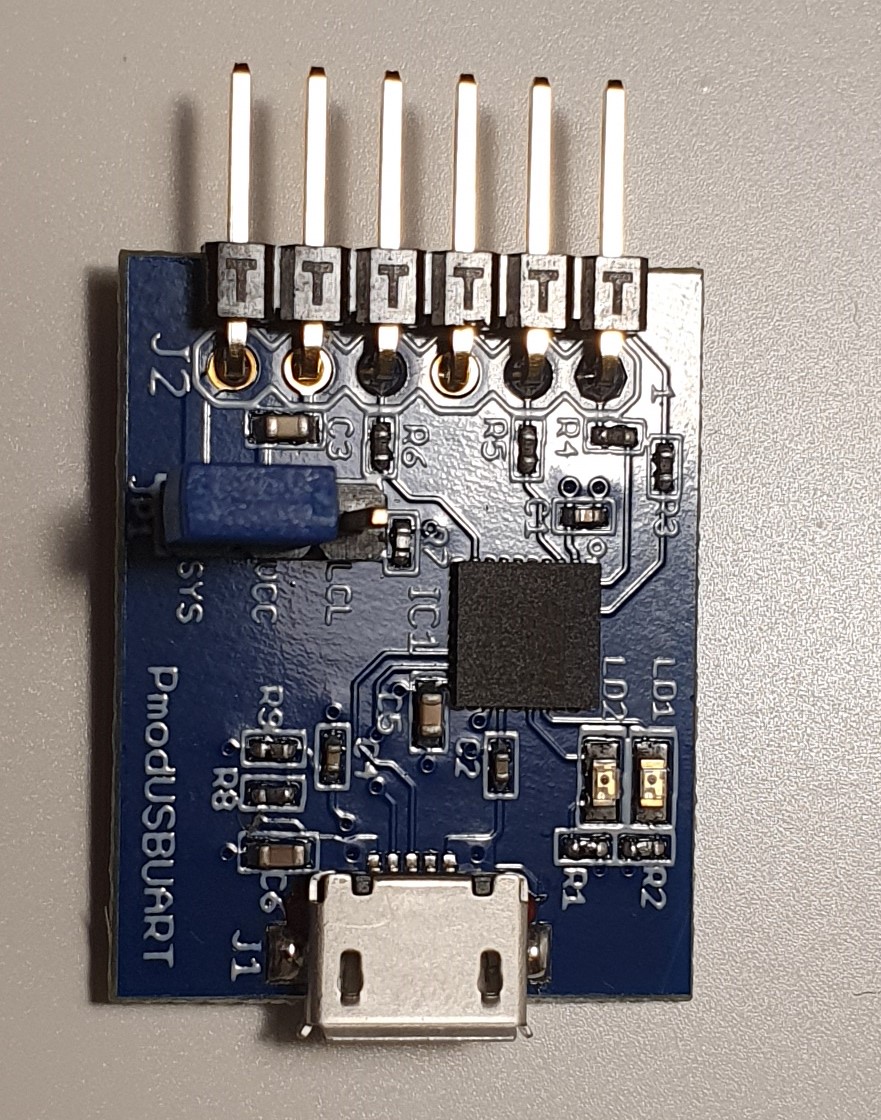

W dostępnych projektach NetFPGA działanie FPGA zależne jest od programowego procesora Microblaze w wersji 8. Programy dedykowane dla tego procesora wykorzystują złącze Pmod układu NetFPGA 1G CML z podłączonym konwerterem dostarczonym w zestawie NetFPGA, jakim jest PmodUSBUART (rysunek 16). Podłączenie FPGA do tego interfejsu zostało przedstawione na rysunku 17.

Rys 16: Konwerter PmodUSBUART

Rys 17: Podłączenie konwertera PmodUSBUART do układu NetFPGA 1G CML

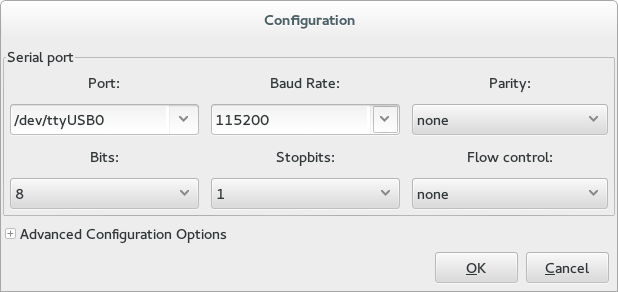

Aby poprawnie odczytywać dane przychodzące należy włączyć oprogramowanie umożliwiające odczyt danych z portu COM i zmienić następujące parametry komunikacji:

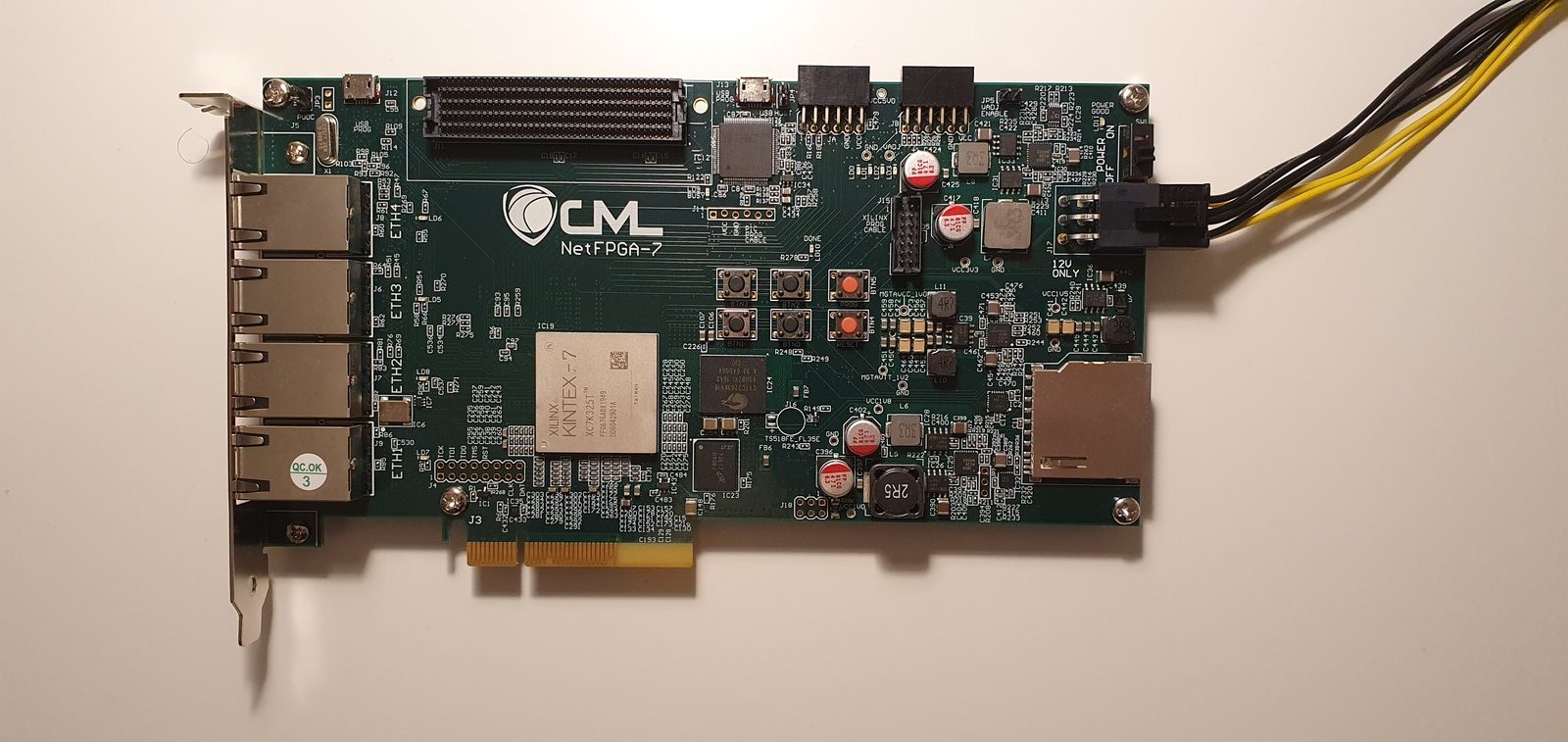

Zasilanie układu NetFPGA jest wyprowadzone na złączu zasilania PCI-E 6 pin. Do złącza należy podłączyć kabel zasilania z zasilacza komputerowego, a następnie przełączyć pozycję przełącznika, znajdującego się obok złącza na pozycję ON. Podłączanie zasilania zostało przedstawione na rysunku 18.

Rys 18: Podłączenie zasilania do układu NetFPGA 1G CML

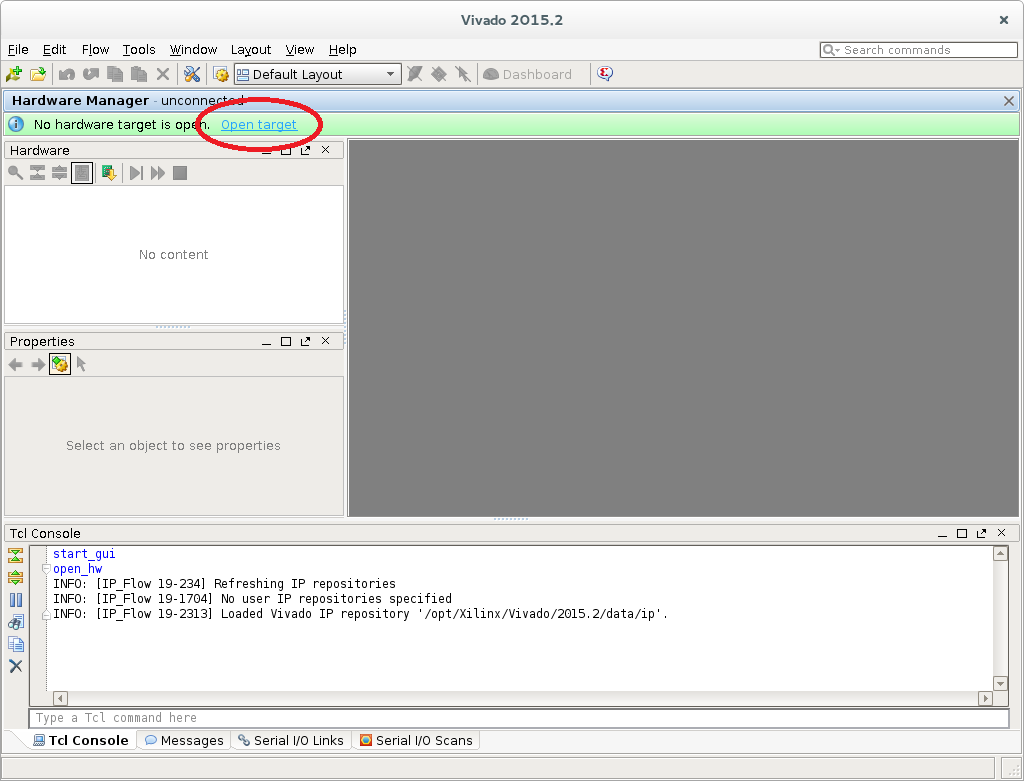

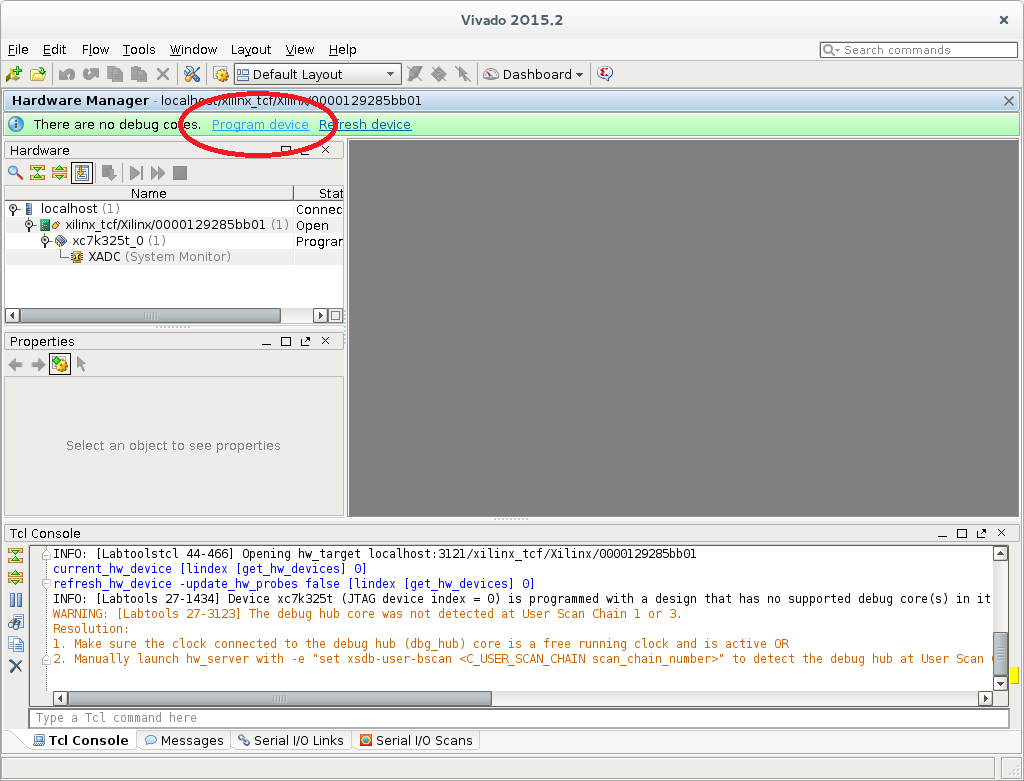

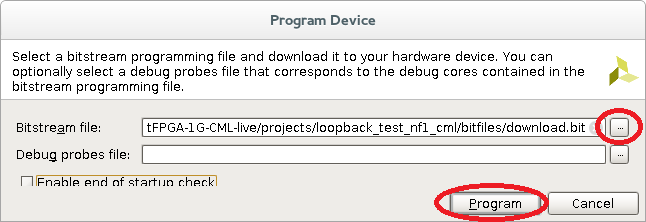

Programowanie układu NetFPGA 1G CML można wykonać za pomocą oprogramowania Vivado oraz programatora, którego podłączenie zostało opisane w rozdziale 1.7.1.1. Po podłączeniu układu i włączeniu zasilania należy uruchomić oprogramowanie Hardware Manager dostępne w Vivado. Następnie należy nacisnąć przycisk Open target i wybrać dostępny układ FPGA. Po wykryciu urządzenia należy nacisnąć przycisk Program device i wybrać plik *.bit. Na koniec należy nacisnąć przycisk Program. Poszczególne kroki instalacji zostały zaprezentowane na rysunku 19.

Rys 19: Programowanie układu NetFPGA 1G CML za pomocą Vivado

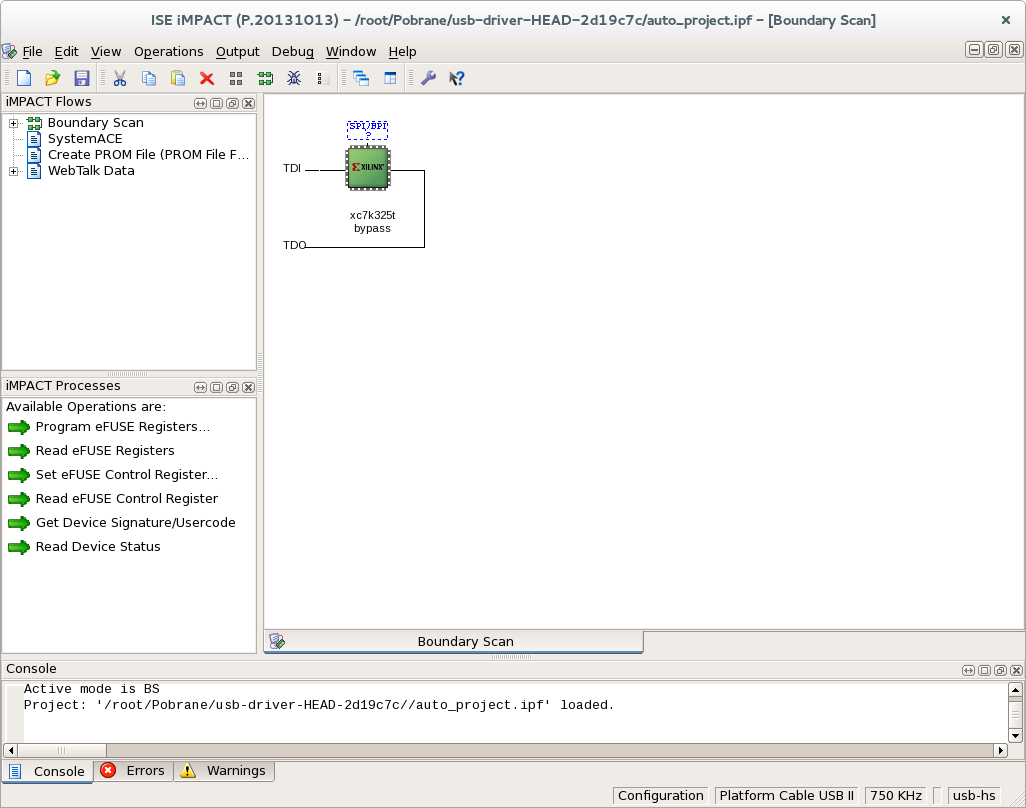

Programowanie układu NetFPGA 1G CML można wykonać za pomocą oprogramowania ISE Design Suite oraz programatora, którego podłączenie opisane zostało w rozdziale 1.7.1.1. Po podłączeniu układu i włączeniu zasilania należy uruchomić oprogramowanie impact za pomocą konsoli:

source /opt/Xilinx/14.7/ISE_DS/settings64.sh

impact

Po wykonaniu komendy należy nacisnąć prawym przyciskiem myszy na wykryte urządzenie, na rysunku 20 oznaczone na zielono, wybrać Assign New Configuration File i następnie wybrać plik *.bit. Po wybraniu pliku należy nacisnąć ponownie prawym przyciskiem myszy na wykryte urządzenie i wybrać Program.

Rys 20: Programowanie układu NetFPGA 1G CML za pomocą ISE Design Suite

System make w projektach NetFPGA posiada komendę umożliwiającą programowanie układu NetFPGA 1G CML. Po zbudowaniu projektu i podłączeniu programatora, którego podłączenie zostało opisane w rozdziale \ref{pod_prog}, należy użyć komendy make download, która uruchomi oprogramowanie Impact i zaprogramuje urządzenie zbudowanym plikiem konfiguracyjnym:

cd $NF_DESIGN_DIR source /opt/Xilinx/14.7/ISE_DS/settings64.sh

make download

Sprawdzenie działania kart Ethernet w układzie NetFPGA 1G CML można wykonać za pomocą projektu Ethernet Interface Loopback Test. W tym celu należy zaprogramować urządzenie plikem konfiguracyjnym wygenerowanym w projekcie Ethernet Interface Loopback Test oraz podłączyć interfejs UART opisany w rozdziale 1.7.1.2. Następnie należy podłączyć pierwszą kartę sieciową do drugiej oraz trzecią do czwartej za pomocą kabli Ethernet.

Rys 21: Podłączenie kart sieciowych układ NetFPGA 1G CML w projekcie Ethernet Interface Loopback Test

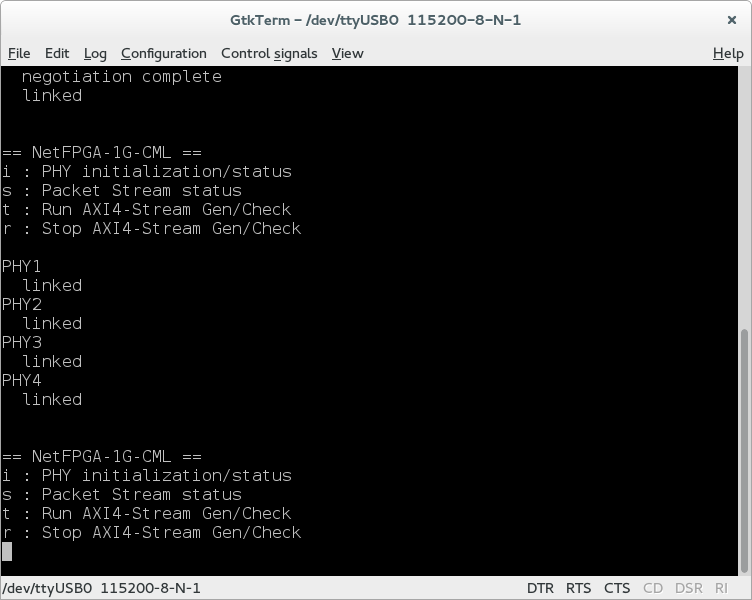

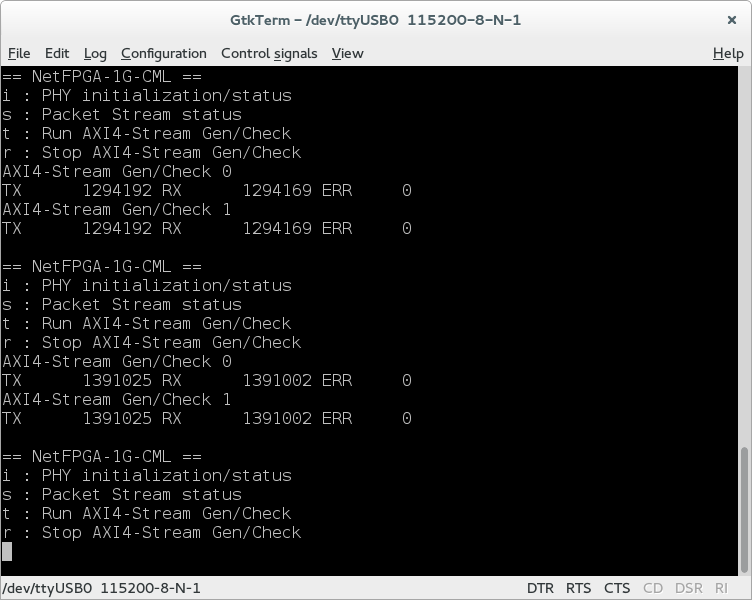

Po zaprogramowaniu układu NetFPGA i podłączeniu interfejsu UART do komputera, możliwa jest komunikacja z kartą za pomocą portu COM. Komunikację można realizować dowolnym oprogramowaniem np. gtkterm z ustawieniem parametrów połączenia na:

Rys 22:Ustawienie parametrów połączenia UART

Po uruchomieniu komunikacji możliwe jest włączanie i wyłączanie przesyłania pakietów pomiędzy kartami Ethernet układu NetFPGA.

Rys 23: Uruchomienie testowania kart za pomocą projektu Ethernet Interface Loopback Test

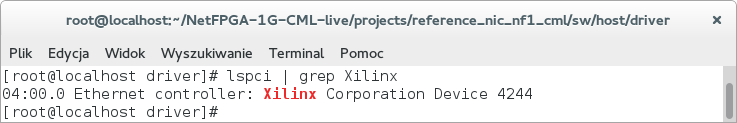

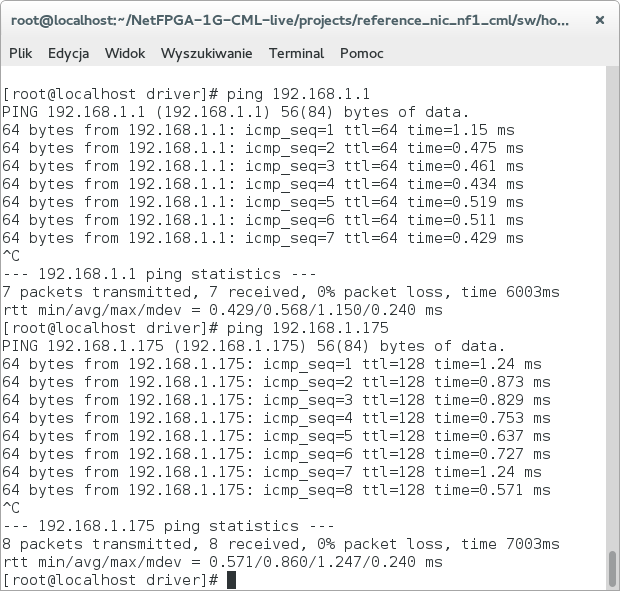

W celu użycia układu NetFPGA 1G CML jako czterech kart sieciowych należy zbudować projekt Reference NIC, a następnie zaprogramować nim układ FPGA. Po zaprogramowaniu należy uruchomić ponownie komputer. Można to zrobić za pomocą następujących komend: export NF_DESIGN_DIR=${NF_ROOT}/projects/reference_nic_nf1_cml cd $NF_DESIGN_DIR make reboot Po uruchomieniu system powinien wyświetlać w liście podłączonych urządzeń do magistrali PCI, kartę NetFPGA. Podłączone urządzenia można sprawdzić za pomocą następującej komendy: lspci | grep Xilinx

Rys 24: Wyświetlenie zaprogramowanego układu podłączonego do PCI-E

Po wykonaniu kroków z rozdziału 1.9.1.1 należy zbudować i zainstalować sterowniki PCI-E dostępne w projekcie Reference NIC. W tym celu należy przejść do folderu drivers, a następnie zbudować i zainstalować sterowniki:

cd $NF_ROOT/projects/reference_nic_nf1_cml/sw/host/driver/

make

sudo insmod nf10.ko

Po wykonaniu kroków z rozdziału 1.9.1.2 należy włączyć karty sieciowe: ifconfig nf0 up ifconfig nf1 up ifconfig nf2 up ifconfig nf3 up

Rys 25: Wyświetlenie kart sieciowych układu NetFPGA

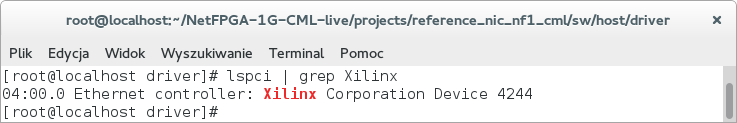

Po wykonaniu kroków z rozdziału 1.9.1.3 możliwe jest przypisanie adresu IP do karty sieciowej NetFPGA. Do pierwszego złącza, znajdującego się najbliżej złącza PCI układu NetFPGA 1G CML, należy podłączyć kabel sieciowy umożliwiając dostęp do sieci. Karta sieciowa urządzenia podłączanego musi obsługiwać połączenie 1Gbit. Następnie należy wykonać przypisanie adresu IP oraz DNS. Przykład konfiguracji:

ifconfig nf0 192.168.1.200 netmask 255.255.255.0

echo ''nameserver 192.168.1.1'' > /etc/resolv.conf

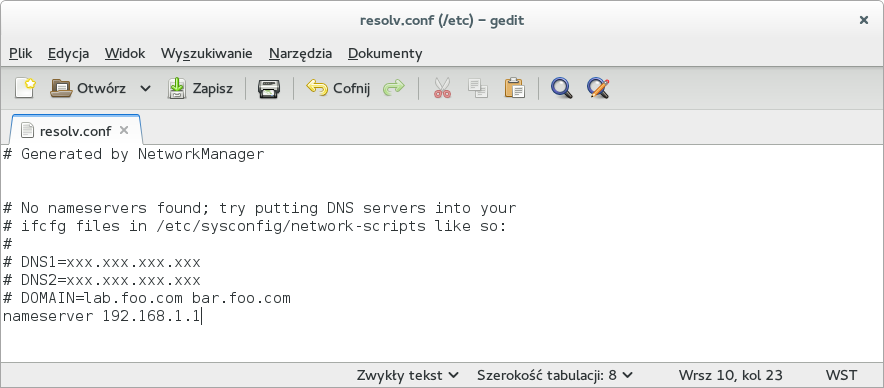

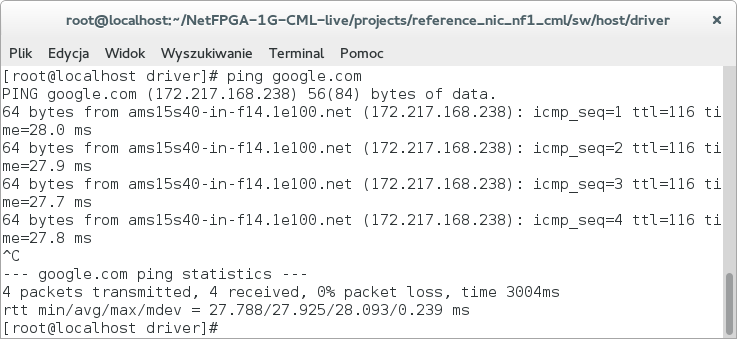

Rys 26: Ustawienie adresów IP oraz DNS \noindent Następnie można wykonać ping sprawdzający komunikację: ping 192.168.1.1 - ping do bramy ping 192.168.1.175 - ping do dowolnego urządzenia w sieci wewnętrznej ping google.com - ping do adresu zewnętrznego

Rys 27: Zrzuty ekranu przedstawiające testowanie połączenia za pomocą komendy ping

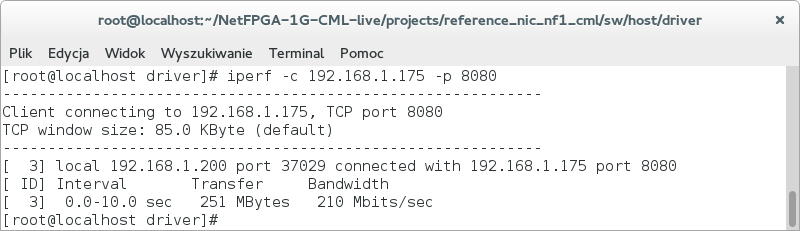

W celu przetestowania działania połączenia należy podłączyć dwa urządzenia do sieci, jedno z podłączonym układem NetFPGA oraz drugie posiadające kartę sieciową. Na drugim urządzeniu należy uruchomić serwer za pomocą iperf. Oprogramowanie dostępne jest pod adresem link Przykład uruchomienia serwera:

iperf -s -p 8080

Następnie można sprawdzić przepustowość połączenia uruchamiając program klienta z komputera z podłączonym układem NetFPGA. Przykład uruchomienia klienta:

iperf -c 192.168.1.175 -p 8080

Rys 28: Testowanie połączenia z innym urządzeniem podłączonym do sieci

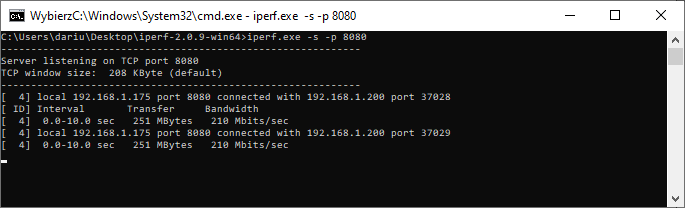

W celu uruchomienia układu NetFPGA 1G CML jako urządzenia switch przełączającego ruch w sieci Ethernet należy zaprogramować układ zbudowanym projektem Learning Switch (Lite). Po zaprogramowaniu urządzenia należy podłączyć do złącz kart sieciowych dowolne urządzenia np. Raspberry PI 4 i ustawić na nich adresy IP.

Rys 29: Podłączenie dwóch urządzeń Raspberry PI 4 do układu NetFPGA z zaprogramowanym Switch'em

W celu sprawdzenia przepustowości połączenia należy podłączyć dwa urządzenia do sieci. Następnie na jednym urządzeniu należy uruchomić serwer za pomocą programowania iperf. Oprogramowanie dostępne jest pod adresem link Przykład uruchomienia serwera:

iperf3 -s -p 8080

Następnie należy sprawdzić przepustowość połączenia uruchamiając program klienta z komputera z podłączonym układem NetFPGA. Przykład uruchomienia klienta:

iperf -c 192.168.1.102 -p 8080

Rys 30: Badanie przepustowości między dwoma urządzeniami Raspberry PI 4 podłączonymi do układu NetFPGA z zaprogramowanym Switch'em

Jeżeli istnieje potrzeba dokonania zmiany działania programów dla programowanego procesora Microblaze, to aby dokonać zmiany w ich działaniu, należy zmodyfikować kod programu dostępnego w każdym z projektów w folderze sw/embedded.

Do poprawnego połączenia sieci Ethernet należy stosować układy wspierające połączenie 1Gbps. Poprawne podłączenie sieci sygnalizowane jest mruganiem diod układu NetFPGA opisanych znakami ETH0, ETH1, ETH2 i ETH3 na PCB układu.

W niniejszym rozdziale przedstawiono wyniki eksperymentów badawczych dla dwóch oprogramowań układu NetFPGA 1G CML.

W podrozdziale przedstawiono wyniki eksperymentów badawczych dla układu NetFPGA 1G CML, zastosowanego jako kartę sieciową.

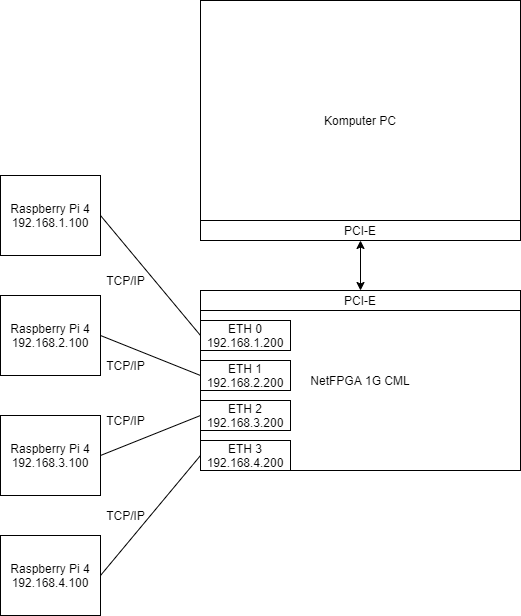

Do badań przygotowane zostało stanowisko badawcze składające się z komputera PC, posiadającego złącze PCI-E na płycie głównej. Do złącza PCI-E komputera PC podłączono układ NetFPGA 1G CML z programem umożliwiającym wykrywanie kart sieciowych podłączonego, układu jako systemowych kart sieciowych. Następnie do kart sieciowych układu NetFPGA podłączono 4 urządzenia Raspberry PI 4, posiadające karty sieciowe o przepustowości 1 Gbps. Do kart sieciowych urządzeń Raspberry PI 4 przypisano następujące adresy IP:

Do kart sieciowych układu NetFPGA 1G CML przypisano następujące adresy IP:

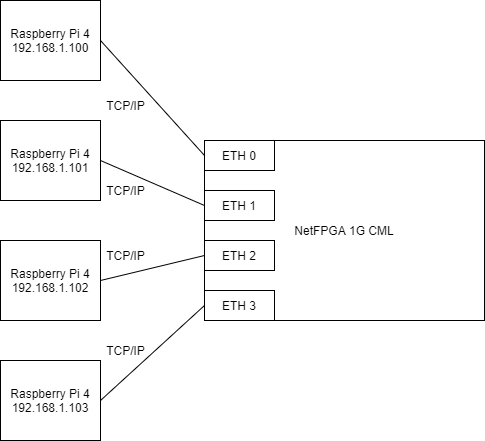

Następnie połączono karty sieciowe zgodnie ze schematem przedstawionym na rysunku 31.

Rys 31: Schemat połączenia urządzeń Raspberry Pi 4 do układu NetFPGA 1G CML

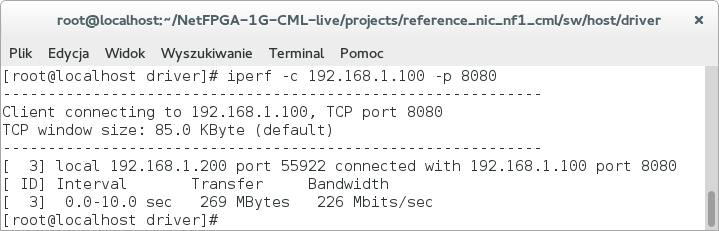

Na każdym urządzeniu uruchomione zostało dedykowane oprogramowanie, umożliwiające badanie prędkości transmisji w sieci Ethernet. Pomiędzy urządzeniem Raspberry Pi 4, a komputerem PC z podłączonym układem NetFPGA 1G CML zmierzono następujące prędkości transferu danych:

Na rysunku 32 przedstawiono zrzut ekranu prezentujący otrzymane wyniki prędkości transferu pomiędzy jednym urządzeniem Raspberry Pi 4, a komputerem PC.

Rys 32: Zrzut ekranu prezentujący prędkość transmisji pomiędzy urządzeniem Raspberry Pi 4, a komputerem PC z podłączonym układem NetFPGA zastosowanym jako karta sieciowa

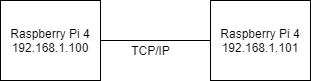

W analogiczny sposób zmierzono prędkości transferu pomiędzy dwoma urządzeniami Raspberry Pi 4 połączonymi bezpośrednio do siebie. Średnia prędkość wyniosła 934 Mbps. Na rysunku 33przedstawiono schemat połączenia obu urządzeń.

Rys 33: Schemat bezpośredniego połączenia dwóch urządzeń Raspberry Pi 4

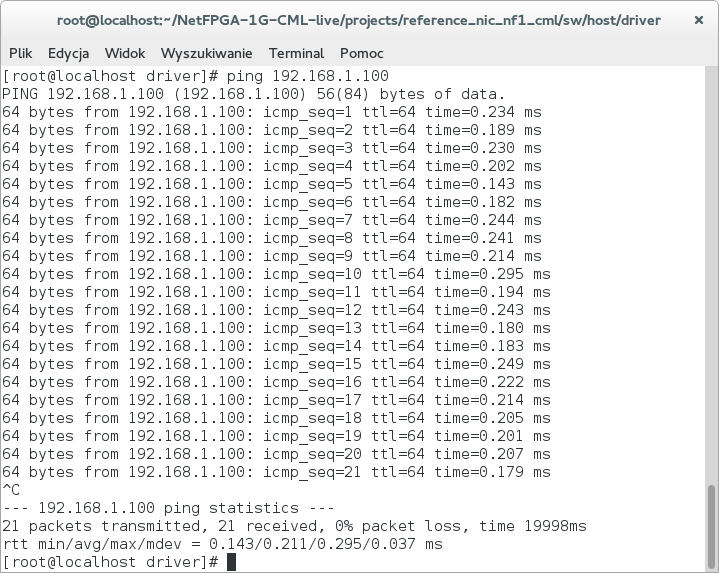

Na każdym urządzeniu uruchomione zostało dedykowane oprogramowanie, umożliwiające badanie opóźnień transmisji w sieci Ethernet. Pomiędzy urządzeniem Raspberry Pi 4, a komputerem PC z podłączonym układem NetFPGA 1G CML zmierzono następujące opóźnienia transmisji danych:

Na rysunku 34 przedstawiono zrzut ekranu prezentujący otrzymane wyniki opóźnienia transmisji pomiędzy jednym urządzeniem Raspberry Pi 4, a komputerem PC.

Rys 34: Zrzut ekranu prezentujący opóźnienie transmisji pomiędzy urządzeniem Raspberry Pi 4, a komputerem PC z podłączonym układem NetFPGA zastosowanym jako karta sieciowa

W analogiczny sposób zmierzono opóźnienia transferu pomiędzy dwoma urządzeniami Raspberry Pi 4. Średnie opóźnienie wyniosło 0.205ms. Na rysunku 33 przedstawiono schemat połączenia obu urządzeń.

Rezultaty przeprowadzonych eksperymentów sieciowych dowodzą poprawności działania oprogramowania umożliwiającego wykrywanie układu NetFPGA 1G CML jako 4 kart sieciowych. Niestety znikoma wiedza literaturowa w tematyce stworzenia podobnych mechanizmów sieciowych na specjalizowanych układach opartych o macierze programowalne FPGA uniemożliwiła zaimplementowanie układu o wydajności rzeczywistych kart sieciowych o przepustowości 1Gbps.

W podrozdziale przedstawiono wyniki eksperymentów badawczych dla układu NetFPGA 1G CML, zastosowanego jako urządzenie do przełączania pakietów (Switch).

Do badań przygotowane zostały dwa stanowiska badawcze składające się z układu NetFPGA 1G CML zaprogramowanego jako urządzenia do przełączania pakietów (Switch) oraz dwóch lub czterech urządzeń Raspberry Pi 4. Następnie do kart sieciowych układu NetFPGA podłączono urządzenia Raspberry PI 4 posiadające karty sieciowe o przepustowości 1 Gbps. Do kart sieciowych urządzeń Raspberry PI 4 przypisano następujące adresy IP:

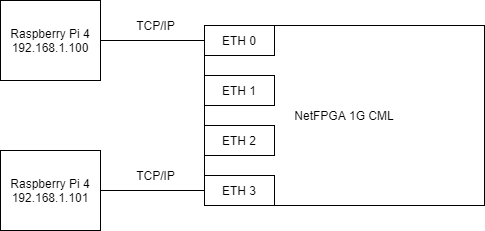

Następnie połączono karty sieciowe zgodnie ze schematem przedstawionym na rysunku 35 dla 4 urządzeń oraz na rysunku 36 dla 2 urządzeń.

Rys 35: Schemat połączenia czterech urządzeń Raspberry Pi 4 do układu NetFPGA 1G CML zaprogramowanego jako urządzenie do przełączania pakietów

Rys 36: Schemat połączenia dwóch urządzeń Raspberry Pi 4 do układu NetFPGA 1G CML zaprogramowanego jako urządzenie do przełączania pakietów

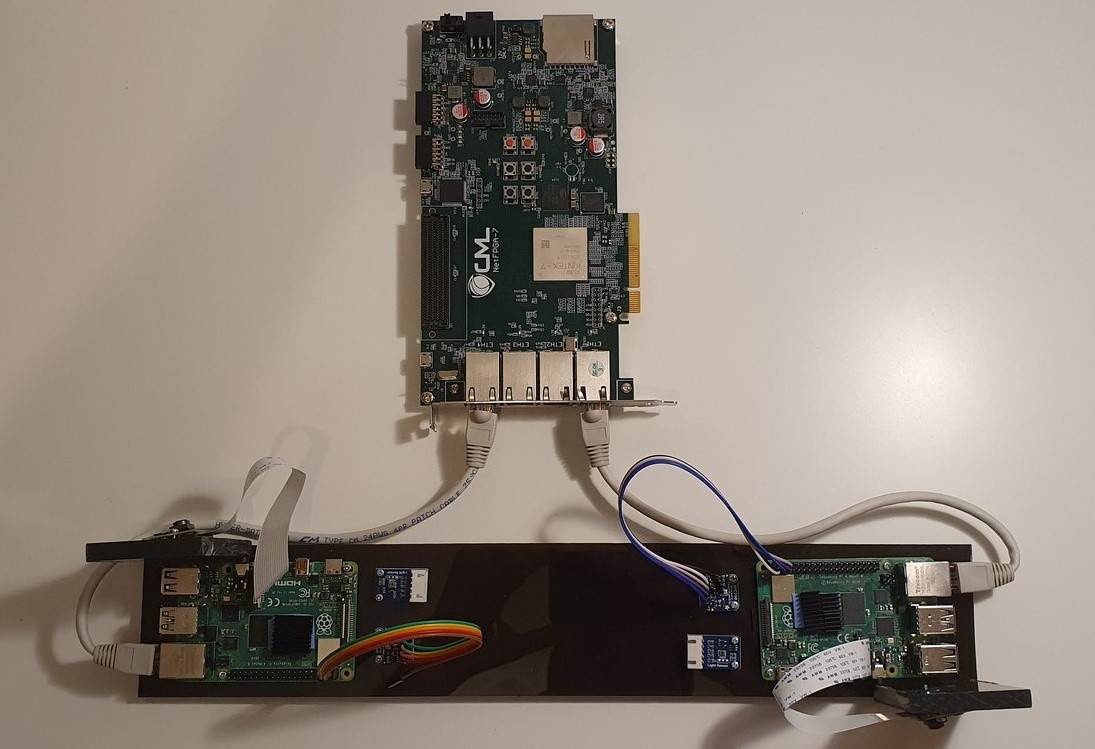

Na każdym z czterech (rysunek 35) urządzeń Raspberry PI 4 uruchomione zostało dedykowane oprogramowanie, umożliwiające przesyłanie pakietów pomiędzy urządzeniami w sieci Ethernet. Sprawdzono poprawność przesyłania pakietów pomiędzy każdym z urządzeń. Rezultaty przeprowadzanych eksperymentów dowiodły poprawność przełączania pakietów pomiędzy kartami Ethernet w układzie NetFPGA. Na rysunku przedstawiono zrzut ekranu prezentujący poprawność przesyłu danych pomiędzy dwoma urządzeniami Raspberry Pi 4.

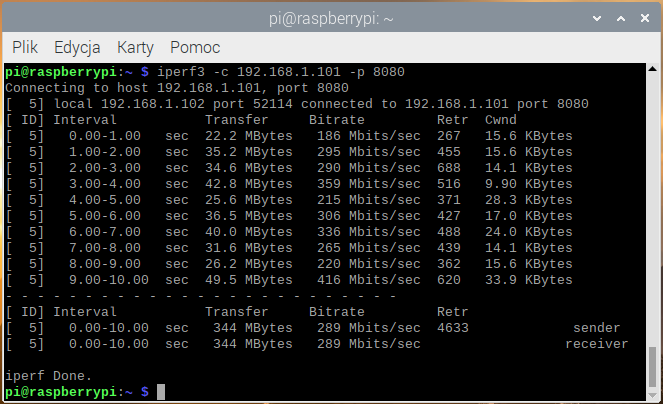

Na każdym z dwóch (rysunek 36) urządzeń Raspberry Pi 4 uruchomione zostało dedykowane oprogramowanie, umożliwiające badanie prędkości transmisji w sieci Ethernet. Zmierzono średnią prędkość transferu danych pomiędzy urządzeniami Raspberry Pi 4, podłączonymi za pośrednictwem układu NetFPGA. Średnia prędkość wyniosła 289 Mbps. W analogiczny sposób zmierzono prędkości transferu pomiędzy dwoma urządzeniami Raspberry Pi 4, połączonymi za pośrednictwem rzeczywistego urządzenia do przełączania pakietów o przepustowości 1Gbps oraz podczas połączenia bezpośredniego. Otrzymane średnie prędkości wyniosły kolejno 905 Mbps i 934 Mbps. Na rysunku 37 przedstawiono zrzut ekranu prezentujący otrzymane wyniki prędkości transferu pomiędzy urządzeniami Raspberry Pi 4, połączonymi za pośrednictwem układu NetFPGA.

Rys 37: Zrzut ekranu prezentujący prędkość transmisji pomiędzy urządzeniami Raspberry Pi 4, połączonymi za pośrednictwem układu NetFPGA

Na każdym z dwóch (rysunek 35) urządzeń Raspberry Pi 4 uruchomione zostało dedykowane oprogramowanie, umożliwiające badanie opóźnień transmisji w sieci Ethernet. Zmierzono średnie opóźnienie transmisji danych pomiędzy urządzeniami Raspberry Pi 4, połączonymi za pośrednictwem układu NetFPGA wynoszące 0.263 ms. W analogiczny sposób zmierzono średnie opóźnienie transmisji pomiędzy dwoma urządzeniami Raspberry Pi 4, połączonymi za pośrednictwem rzeczywistego urządzenia do przełączania pakietów o przepustowości 1Gbps oraz podczas połączenia bezpośredniego. Otrzymane średnie opóźnienia transmisji wyniosły kolejno 0.248 ms i 0.205 Mbps. Na rysunku 38 przedstawiono zrzut ekranu prezentujący otrzymane wyniki prezentujące opóźnienie transmisji pomiędzy urządzeniami Raspberry Pi 4 podłączonymi za pośrednictwem układu NetFPGA.

Rys 38: Zrzut ekranu prezentujący opóźnienie transmisji pomiędzy urządzeniami Raspberry Pi 4, połączonymi za pośrednictwem układu NetFPGA

Rezultaty przeprowadzonych eksperymentów sieciowych dowodzą poprawności działania układu NetFPGA 1G CML, zastosowanego jako urządzenie do przełączania pakietów (Switch). Otrzymane prędkości transmisji danych jak i czasy opóźnień niestety okazały się gorsze od wartości otrzymanych przy połączeniu układów za pośrednictwem rzeczywistego urządzenia do przełączania pakietów. Znikoma wiedza literaturowa w tematyce stworzenia podobnych mechanizmów sieciowych na specjalizowanych układach opartych o macierze programowalne FPGA, nie umożliwiła zaimplementowania rozwiązania o wydajności rzeczywistych urządzeń.

Rezultaty dotychczas wykonanych prac nie są na tyle zadowalające, aby móc je opublikować na międzynarodowej konferencji, bądź w wysoko punktowanym czasopiśmie.

Wykonana praca stwarza jednak nowe możliwości badawcze w tematyce wykorzystania macierzy FPGA w sieciach komputerowych. Kolejne prace wykonywane w ramach realizacji projektów Studenckiego Koła Naukowego, czy też prac magisterskich nawiązywać mogą do zagadnień implementowania algorytmów aktywnego zarządzania kolejką w węźle komunikacyjnym, czy też do badania ich zachowania w rzeczywistym układzie. Bez obecnie wykonanego kroku, który umożliwia przechwytywanie przychodzących pakietów oraz pozwala przełączać pakiety pomiędzy kartami sieciowymi, nie można było by zakładać powodzenia realizacji takich badań.

© Politechnika Śląska

Całkowitą odpowiedzialność za poprawność, aktualność i zgodność z przepisami prawa materiałów publikowanych za pośrednictwem serwisu internetowego Politechniki Śląskiej ponoszą ich autorzy - jednostki organizacyjne, w których materiały informacyjne wytworzono. Prowadzenie: Centrum Informatyczne Politechniki Śląskiej (www@polsl.pl)

„E-Politechnika Śląska - utworzenie platformy elektronicznych usług publicznych Politechniki Śląskiej”